基于FPGA的高速數據采集控制模塊設計

摘要 以Spartan-3E系列FPGA為核心控制模塊,結合AD10242模數轉換芯片和MXP-123MD-F光收發模塊,實現了高速數據采集和光纖傳輸 其中FPGA用于實現數據控制、雙口RAM和8B/10B編解碼等功能。該數據采集控制模塊具有性能可靠、實時性強、集成度高、擴展靈活等特點,并且通過試驗驗證了其功能的正確性。

關鍵詞 數據采集;FPGA;8B/10B編解碼;光纖傳輸

在雷達、通信、氣象、軍事監控及環境監測等領域,現場信號具有重要的作用。這些信號的主要特點是:實時性強、數據速率高、數據量大、處理復雜。為能夠完整、準確地捕獲到各種信號并及時進行處理,需要臨測系統能夠具備任意長度連續采集和存儲的功能,且具有較高的數據傳輸率。考慮到FPGA擁有豐富的可編程I/O引腳、時鐘頻率高、時序控制精確、運行速度快、編程配置靈活等特點,采用其作為核心控制模塊。因為光纖通信使用簡單的點到點互連,具有傳輸損耗低、傳輸頻帶寬、速率高和抗電磁干擾等優點,在增加可靠性的同時降低了電纜連接的復雜程度,所以采用光纖作為信號傳輸媒介。

這里設計的數據采集控制模塊能夠對8通道模擬信號進行兩種不同頻率的采集,采集時間的長短町以進行控制,并對數據進行了編幀,編解碼處理,利用光纖進行數據傳輸。

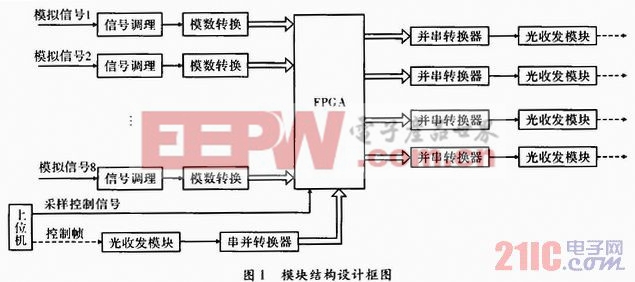

1 模塊結構設計方案

8通道的模擬信號經過信號調理、A/D模數轉換電路后進入FPGA。上位機發送的控制幀經光收發模塊、串并轉換器后進入FPGA,作為采集數據的幀頭部分,該幀中有1 Byte決定了采樣的頻率。上位機向FPGA發送采樣控制信號:采樣導前信號以及采樣時間長度信號。在FPGA中將8通道采集的數據以兩通道為一組分成4份分別與幀頭打包組幀,存入雙口RAM,編碼處理后經過并串轉換器、光收發模塊發送出去。模塊結構設計框圖如圖1所示。

評論