基于Wishbone和端點IP的PCIE接口設計

摘要:介紹了FPGA內嵌的PCI Express硬核端點模塊和Wishbone片上總線規范。應用VHDL語言,編程實現了Wishbone總線的主從端口,以及TLP包的編碼和解碼功能。在FPGA上運行程序并使用Chipscope測試時序波形,驗證了接口數據傳輸的穩定性和正確性。

關鍵詞:PCI Express總線;FPGA;PCIE端點模塊;Wishbone

0 引言

當前,基于FPGA實現PCI Express接口有兩種方案,一是采用第三方PHY接口器件和FPGA實現;二是采用集成GTP的FPGA來實現。集成GTP的FPGA實現PCI Express接口在鏈路效率、兼容性測試及資源可用性等方面有其獨特的優勢。隨著技術的發展和對傳輸數據速率和靈活性要求的提高,將更加趨于利用高性能FPGA(即集成GTP的FPGA)來實現PCIExpress接口功能。但是,要在FPGA上實現PCI Express通信橋接,還需要用戶根據PCI Express協議構建自己的軟IP或者向第三方或FPGA供應商購買IP核。構建IP核的難題在于其難度較大且開發周期較長;向第三方或FPGA供應商購買的IP,存在專利費用問題。對于一些驗證性開發,其重點一般在于應用功能的實現,而希望公共模塊(如PCI Express接口)的開發在滿足性能的前提下,盡量少花時間和費用,從而縮短開發周期和成本。因此,利用已有可獲取資源,實現PCI Express接口成為這類開發中的首選。

Xilinx的V5/V6系列FPGA芯片中已集成了硬核端點的PCI Express模塊,提供了PCI Express接口的底層配置,相當于提供了一個專用協議與PCI Express之間的橋梁。在PCI Express硬核端點上集成片上總線,實現PCI Express與應用模塊互聯,將能更快地實現PCI Express接口的開發。

目前比較常見的片上總線規范有IBM公司的CoreConnect,ARM公司的AMBA和Silicore Corp公司的Wishbone。CoreConnect和AMBA規范復雜,在設計中需要建立連接橋以連接不同IP核。相對于其他兩種接口規范,Wishbone接口規范具有簡單、高效、易于實現等特點,而且完全免費。因此,本文采用Wishbone總線規范實現PCI Exprpess接口。

1 Wishbone基本原理、Xilinx集成端點IP及TLP包結構

1.1 Wishhone的基本原理

Wishbone最先是由Silicore公司提出的,現在己被移交給OpenCores組織維護。其開放性、簡單性和靈活性受到廣大設計者的青睞,現在己有不少的用戶群體,特別是一些免費的IP核,采用Wishbone標準。除了具備地址/數據總線寬度可變、互聯結構可變及仲裁機制靈活等片上總線的共同特點外,Wishhone還包括以下特征:

(1)支持點到點、共享總線、十字交叉和基于交換結構的互聯;

(2)支持常用的總線數據傳輸協議,如單字節讀寫周期、塊傳輸周期、控制操作及其他的總線事務等;

(3)主/從結構,支持多控制器和64位地址空間,從端部分地址解碼;握手協議使得每個核都可以控制數據的傳輸速度;

(4)用戶自定義標記(TAG),確定數據傳輸類型、中斷向量等;

(5)接口簡單、緊湊,總線實現的邏輯單元少。

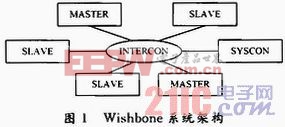

Wishhone采用主端(Master)和從端(Slave)的架構。主端模塊發出數據傳送請求,然后通過一個接口網絡和從端進行數據交換,其系統結構如圖1所示。這個接口網絡稱之為INTERCON,各終端之間訪問通過INTERCON,INTERCON內部可根據訪問情況采用不同的互連方式,Wishbone將它稱為可變互聯網絡。可變互聯網絡的連接形式有點對點、數據流、共享總線和交叉總線等。

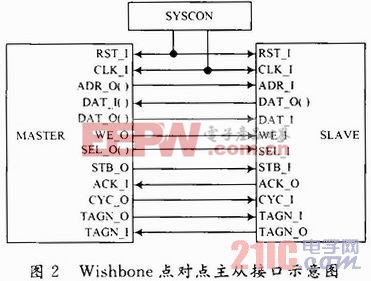

Wishbone可變的互連方式允許系統設計工程師可以采用不同的IP核互連方式,以滿足不同場合的要求。根據需要,本設計采用點對點的總線互連方式。圖2給出了點對點的MASTER/SLAVE主從接口圖。其中SYSCON為產生時鐘和復位信號,TAGN為用戶自定義信號。

評論