基于Spartan-3 FPGA的視頻采集系統設計

引言

本文引用地址:http://www.j9360.com/article/189987.htm視頻采集的主流實現方案有兩種:一是基于ASIC,該方案一般采用意法、AMD等公司的專用視頻處理芯片;二是基于DSP,主要采用TI、ADI等公司的DSP信號處理器。它們作為輔處理器,可在主CPU控制下進行視頻信號的采集壓縮。隨著FPGA的發展,通過SOPC技術實現視頻采集已成為一種易于開發、設計靈活的方案。而這主要得益于IP復用技術的發展。在FPGA上構建復雜嵌入式系統可利用既有的功能模塊及其驅動程序。該方案具有更大的集成度和靈活性,因而必將成為電子設計發展的一大趨勢。

本文介紹了采用Xilinx公司的Spartan-3 FPGA實現通用視頻采集系統的設計方案。該系統外接模擬PAL/NTAL制式的攝像頭,就能實時采集視頻信號并進行MPEG-4格式壓縮編碼,碼流可通過USB接口傳給PC機,或通過以太網接口進行網絡傳輸。本系統選用的是Spartan-3 FPGA系列的XC3S200芯片,該芯片有4320個邏輯單元(LC)、216Kbit BlockRAM、4個數字延遲鎖相環(DDL)、173個用戶I/O,而且邏輯密度高、I/O多、成本低。本設計主要涉及電路板級硬件設計、FPGA片級硬件系統設計和系統軟件設計。

1 板級硬件設計

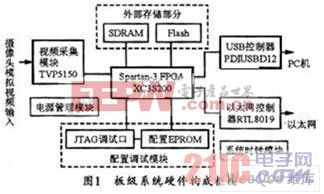

FPGA在電源和配置電路的支持下,即可構成嵌入式系統的最小化系統,并能實現片內的所有功能。在此最小化系統上,就可以根據本設計的應用需求,來擴展外部存儲模塊、視頻采集模塊、USB接口模塊、以太網接口模塊等功能模塊電路,從而形成電路板級硬件平臺。該板級硬件平臺的結構組成如圖1所示。

1.1 最小化系統

該FPGA是基于SRAM存儲結構的器件。每次上電時可將配置數據從外部配置存儲器加載到內部SRAM中,以使其構建邏輯結構從而實現邏輯功能。配置調試模塊主要包括配置存儲器、配置模式跳線開關和JTAG調試端口,其中JTAG調試端口是系統開發階段PC機與FPGA的通信接口,可用于從PC機下載FPGA配置數據,并在程序調試階段作為聯機接口。本設計采用Xilinx公司Platform. Flash系列配置存儲器XCF02S,并采用14針JTAG接口。模式跳線開關可決定FPGA是由JTAG還是由配置存儲器來進行配置。系統時鐘模塊可對XC3S200提供50 MHz高頻時鐘信號,它采用高穩定性的石英晶體振蕩器分立元件。電源管理模塊采用DC/DC變換器來為系統各元件提供需要的各種電壓電流。以上部分與FPGA芯片相連即可構成嵌入式系統工作的最小化系統。

1.2 外部存儲擴展

由于XC3S200的片內存儲容量有限且掉電即失,因此必須配置大容量的外部儲存器。本設計擴展了4MByte的flash和32MByte的SDRAM (包括一片AMD公司的AM29LV320DT90EC型Flash和兩片HYNIX公司的HY57V281620HCT-PI型SDRAM)。其中Flash在系統中用于存放程序代碼、常量表以及一些在系統掉電后需要保存的用戶數據。而SDRAM掉電數據即失,但其存取速度大大高于Flash且可讀可寫,因而在系統中用作程序的運行空間、臨時數據及堆棧區等。

評論