基于FPGA的高精度時差測量系統設計

3 時差測算單元設計

3.1 設計思想

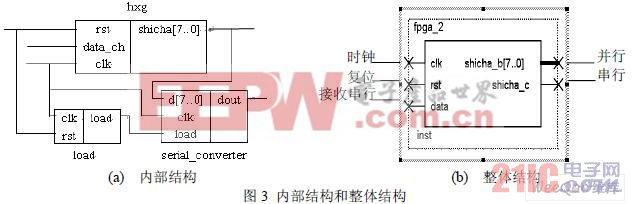

FPGA 作為時差測算單元的核心器件,主要完成相關匹配、并/串轉換、接口控制等功 能,經過VHDL 編程生成的內部結構和各個模塊綜合以后的整體結構如圖3 所示。

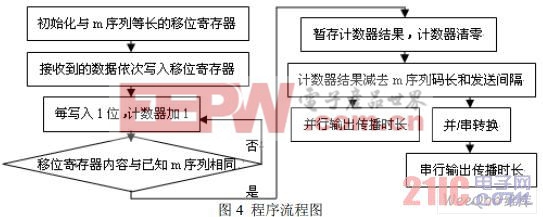

其中,hxg 模塊通過互相關的方法測算出不同路徑的傳播時長,采用8 位并行輸出; serial_converter 模塊把hxg 模塊的結果轉換成串行輸出;load 模塊作為serial_converter 模塊 的使能輸入,當load 有效時并行數據被存儲到移位寄存器中。程序流程圖如圖4 所示。

3.2 實現結果

以 5 級的m 序列為例,反饋系數為45(八進制),初始狀態為10000,得到31 位的m 序 列為1000010010110011111000110111010。碼速率為1Mbps,固定發送間隔為100000 碼元, 即100ms,總共發射4 組m 序列,因此參考圖2 可知能夠測得3 個傳播時長。下圖中的并行輸出結果均用十進制顯示。整體結果和局部放大結果如圖5 所示,仿真結果表明并行結果 與串行結果完全一致。

評論