OFDM系統中頻域同步技術及FPGA實現

細定時同步估計的電路仿真

圖中的data_re_in[15..0]和data_im_in[15..0]表示經公共相位校正后的復數據實虛部;syn_in是輸入有用數據的起始位置脈沖;sym_type[1..0]是前端輸入的符號類型;taok[22..0]和td[9..0]分別為估計的符號定時偏移和其整數部分;syn_tao是taok[22..0]的有效數據起始脈沖信號。

圖4.3 符號定時偏移估計單元的電路波形圖

圖4.3中共有9個符號。由于本算法利用了4個符號的散布導頻,故圖4.3中,從第四個符號的結束處開始,在syn_tao后的taok[22..0]才是當前符號的定時偏移估計值。波形中的估值與實際數據的對應關系如表4.2所示。

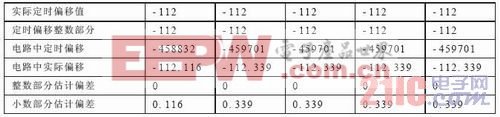

表4.2 波形圖中數據與實際數據對照表

表4.2中的定時實際偏移為-112,而不是仿真條件中的-100,這是由于在瑞利信道的仿真模型中,符號定時同步頭位置(重心位置)是在第一條徑之后12個采樣點出現的。由表中數據對應關系可知,符號定時偏移估計單元可準確地估出符號定時偏移的整數部分。由于采樣鐘偏移、算法估計誤差及電路運算誤差的影響,其小數部分不為零,這與電路的仿真結果一致。

改進前后占用硬件資源比較

表4.3給出了改進前后,頻域同步所占用的硬件資源比較,其中ALUTS、Registers、Memorybits、DSPblock9-bitelements分別為自適應查找表、寄存器、存儲器和9字節DSP處理塊。通過比較可以發現,改進后的方案可以節省大量的硬件資源。

表4.3 改進前后的硬件資源對比

結束語

頻率偏移估計可以分為整數倍頻偏估計單元、小數倍頻偏、采樣鐘偏移估計單元和符號定時偏移估計單元。本文主要介紹各部分的算法方案及電路實現時所用的FPGA元件的基本結構、設計思路。最后通過對電路的仿真波形可以看出,這些頻域同步算法和FPGA電路能夠滿足多載波傳輸系統的同步要求。

評論