基于CPLD及DDS的正交信號源濾波器的設計

1 引言

本文引用地址:http://www.j9360.com/article/189836.htm由于傳統的多波形函數信號發生器需采用大量分離元件才能實現,且設計復雜,這里提出一種基于CPLD的多波形函數信號發生器。它采用CPLD作為函數信號發生器的處理器,以單片機和CPLD為核心,輔以必要的模擬和數字電路,構成的基于DDS(直接數字頻率合成)技術、波形穩定、精度較高的多功能函數信號發生器。

2 系統設計

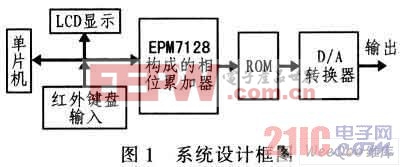

圖1給出系統設計框圖,該系統設計主要由CPLD電路、單片機電路、鍵盤輸入液晶顯示輸出電路以及D/A轉換電路和低通濾波器等電路組成。

2.1 頻率合成器

該系統設計采用直接數字式頻率合成DDS(Direct Digital Frequency Synthesis)技術,采用ROM存儲所需的量化數據,按照不同頻率求出頻率控制字。以K為步進對相位累加器進行累加,每累加一次,取出累加器的高8 位數據送至ROM,ROM根據不同的地址取出不同的數據送TLC7524進行轉換。再經過濾波即可得到所需要波形。由于DDS具有相對帶寬很寬,頻率轉換時間極短,頻率分辨率高等優點。此外,全數字化結構便于集成,輸出相位連續,頻率,相位和幅度均可實現程控。

2.2 幅度控制模塊

幅度控制模塊由DAC0832控制,利用其內部電阻分壓網絡,將其作為數控電位器。將 TLC7524的輸出波形作為DAC0832的基準電壓源輸入,其輸出波形為V=(N/256)×Vin,其中N為單片機輸入的幅度控制字。通過一簡單的電阻分壓網絡調整運放輸出峰一峰值為0~5 V,再送至DAC0832由單片機控制其幅度實現幅度的步進,如圖2所示。

2.3 后級處理模塊

采用二階巴特沃茲低通濾波器。巴特沃茲低通濾波器的幅度函數是單調下降的,由于n階低通巴特沃茲低通濾波器的前(2n-1)階導數在ω=0處為零,所以巴特沃茲低通濾波器也稱最大平坦幅度濾波器。由于該設計要求濾除的頻率分量主要為由D/A轉換器產生的高頻分量,與系統所要求保留的頻率相差很遠,所以濾波器在通頻帶內的平坦程度比其衰減陡度更為重要,而且巴特沃茲低通濾波器所要的元件值合乎實際情況,不像其他濾波器要求元件值那么苛刻。

3 硬件電路系統設計

3.1 總體設計思路

整個系統以CPLD(EPM7128)、AT89S51、AT28C64(EEP-ROM)為核心。CPLD通過相位累加產生讀取ROM的地址。以單片機為系統控制的核心,主要功能:給CPLD送頻率控制字,即相位累加器的累加值,以此控制頻率;給D/A轉換器送幅度控制字D,控制波形幅度;處理紅外遙控鍵盤;送數據給液晶LCD。EEPROM存儲已固化好波形的數據。

評論