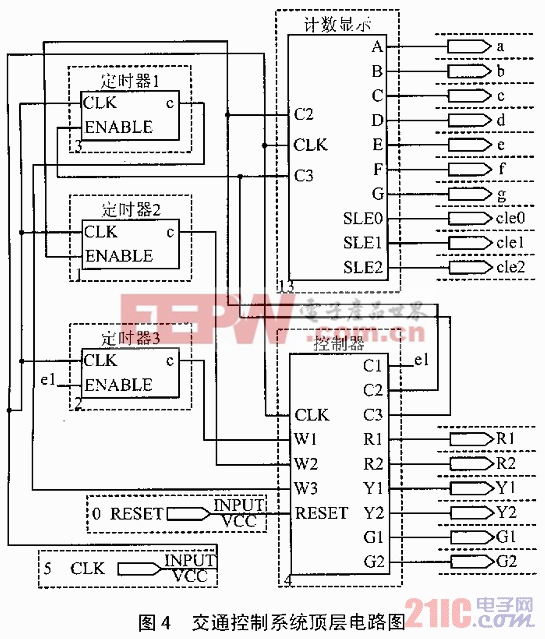

應用CPLD實現交通控制系統芯片設計

3 功能編譯、設計仿真與硬件下載

本系統采用Altera公司生產的FLEX10K系列的CPLD芯片,應用該公司的MAX+PLUS

II開發軟件完成設計后,需對各種源文件從低層到頂層逐個編譯,再進行邏輯仿真。選擇器件后,打開檢查項目中所有設計文件,通過檢測發發現在編程器件中可能存在的可靠性不好的邏輯器件引腳分配。Altera公司推薦的編譯器可自動為項目進行引腳分配,也可人工調整引腳。在編譯器窗口選擇Start按鈕,將對所有設計的項目進行處理,出現錯誤將給出具體錯誤提示。為了保證設計的正確性,在編譯通過后,還需進行邏輯仿真。仿真通過后再應用MAX+PLUS

II的編程器對所選可編程邏輯器件下載編程,便完成了交通控制系統的ASIC芯片設計和硬件固化。若在芯片外圍接入必要電源、脈沖信號、顯示器和指示燈,便構成了一個完整交通控制系統。它具有工作穩定、體積小、在線修改方便等特點。

評論