基于FPGA的彩屏控制器設計

觸摸屏技術方便了人們對計算機的操作使用,是一種極具發展前途的交互式輸入技術,受到各國的普遍重視,并投入大量的人力、物力對其進行研發,使得新型觸摸屏不斷涌現[1]。特別是四線電阻式觸摸屏具有制造工藝簡單、成本低廉、使用方便等特點,已經被廣泛應用于不同的電子設備[2]。

本文引用地址:http://www.j9360.com/article/189671.htm隨著嵌入式技術的高速發展,尤其是CPLD/FPGA的出現,其基于SoPC技術的IP核的使用給開發人員帶來了諸多方便。但在SoPC中并沒有彩色觸摸屏的IP核,因此需要自己編寫硬件的時序控制[3]。本文提出一種基于FPGA的彩色觸摸屏控制器的設計方案,通過單片FPGA芯片可以實現彩色觸摸屏的驅動邏輯,從而實現硬件上時序控制,在此控制器的基礎上可以進一步開發彩色觸摸屏的IP核。

1 彩色觸摸屏控制器的設計

1.1 總體結構及其工作原理

彩色觸摸屏控制器的總體結構如圖1所示。

該彩色觸摸屏的控制器主要由TFT-LCD控制器和ADS7843芯片控制器兩部分組成。由圖1可以看出,TFT-LCD控制器的作用是將圖像數據采集后,通過SDRAM進行緩沖,然后將圖像數據輸出給TFT-LCD。它的主要功能是完成圖像數據的采集和緩沖、TFT-LCD的時序控制及最終數據在TFT-LCD上的顯示。

1.2 TFT-LCD控制器的設計

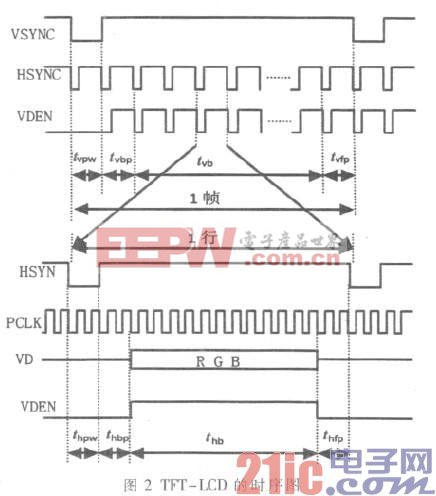

圖像數據經采集和緩沖之后,通過TFT-LCD的時序控制可以將數據按如圖2所示時序圖進行輸出。本設計中采用的TFT-LCD的分辨率為480×272,其RGB數據位均為8 bit,可以顯示16 777 216種顏色。其中,PCLK為LCD像素時鐘信號,HSYNC為行同步信號,VSYNC為幀同步信號,VDEN為數據使能信號,VD[23:0]為LCD像素數據輸出端口,tvpw、tvp、tvbp、tvfp分別為垂直同步脈沖、垂直掃描時間、垂直后回歸、垂直前回歸,thpw、thp、thbp、thfp分別為水平同步脈沖、水平掃描時間、水平后回歸、水平前回歸[4]。

從圖2所示的時序圖可以看出,當HSYNC電平由低變高,再經過水平回歸時間之后,開始進行水平掃描。在水平掃描中,像素的顯示受PCLK控制,一個PCLK周期決定了一個像素點的顯示。在HSYNC的高電平的驅動下,PCLK將產生480個時鐘周期,使圖像的像素點在屏幕上從左向右依次逐點輸出,完成一行共480個像素點的顯示。用Verilog HDL編寫的水平同步掃描的時序程序如下:

評論