可將數據轉換器IP成功集成到系統芯片的12種設計技

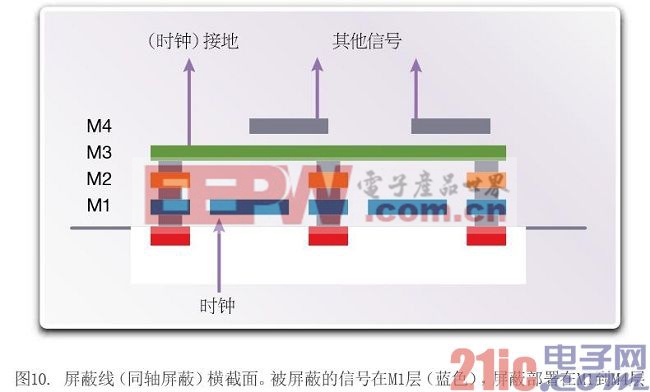

技術10:將時鐘信號與攻擊信號屏蔽開

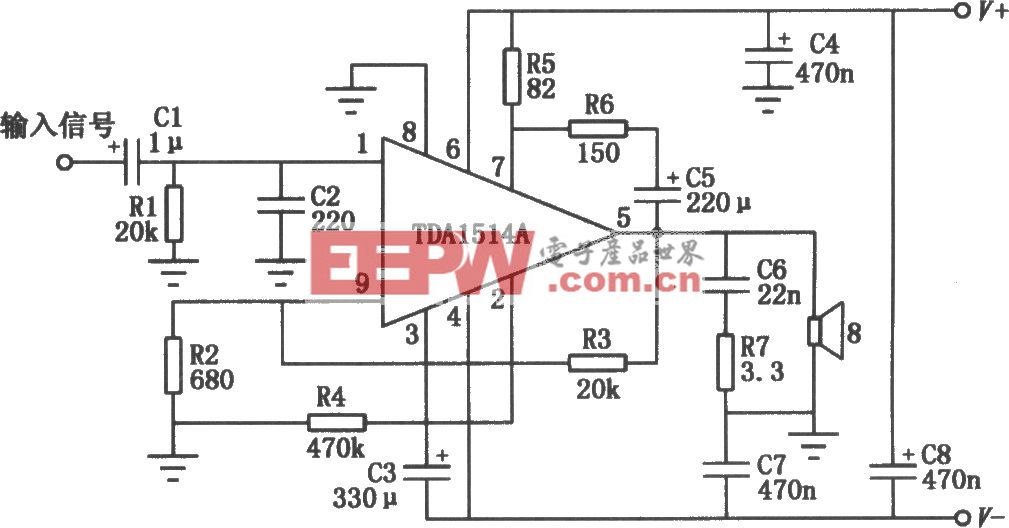

將時鐘信號與攻擊信號屏蔽開,目的是避免噪聲與時鐘耦合并減少抖動。圖10介紹了一種屏蔽信號的方法。在圖中,信號路徑為M1(藍線),在各個方向與電路中的其他信號屏蔽開。屏蔽層通常與時鐘網絡相同的接地電位連接。

4. 保持電源和接地電源干凈

任何模擬電路的電源抑制比(PSRR)都是有限的。電源和接地電源噪聲過大可能影響性能。處理寬帶信號時更是如此,原因是低頻率時抑制比高,但高頻率時抑制比自然會降低。因此,模擬電源應保持干凈,并且使用時應正確去耦合電容。

還有些其他影響,如布線電阻過大可能導致直流(DC)電壓壓降超出數據轉換器工作范圍,還可能造成交流(AC)電壓響應數據轉換器的自生紋波噪聲變慢,可以采用以下技術。

技術11:保持電源和接地布線電阻夠小

設計師應遵循數據轉換器廠商的建議,使電源和接地布線電阻在限制范圍內。這些限制的目的是確保數據轉換器的電流消耗造成的壓降不會使電源電壓超出IP的工作范圍。此外,如前面所解釋的,走線電阻會使自生紋波響應變慢。

技術12:使用專用的電源布線

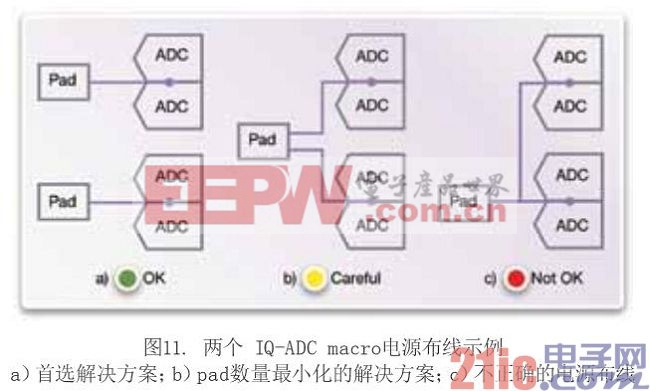

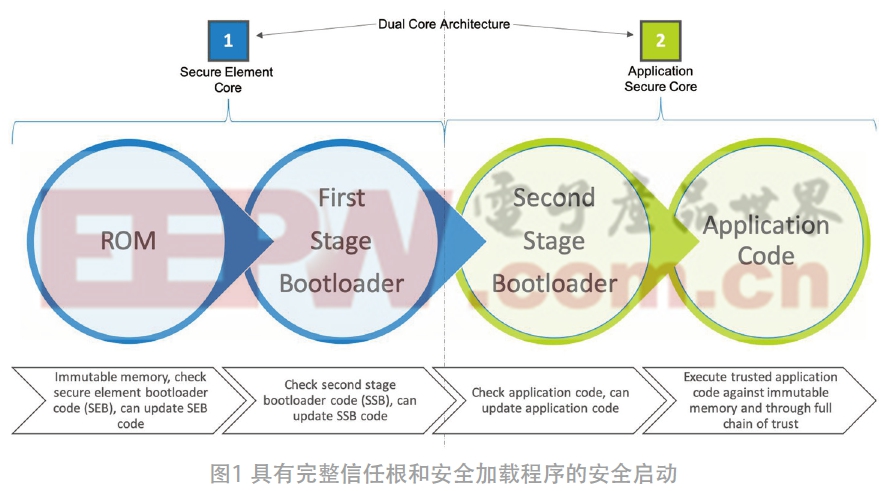

集成多個數據轉換器時,設計師應使用專用電源布線,至少包括IO電源。圖11a解釋了兩個IQ-模擬-數字轉換器情況下的要求。

對于pad數量受限的系統,只要數據轉換器使用相同的時鐘頻率和相位,多個數據轉換器就可以共用相同的IO電源(如圖11b所示)。布線必須與I/O電源(采用星形連接)隔離,并保持電源分布對稱。圖11c圖示說明了不正確的電源分布。在這個例子中,電源分布沒有保持對稱,造成性能降低和串擾。

結論

任何模擬電路的電源抑制比(PSRR)都是有限的。電源和接地電源噪聲過大可能影響性能。處理寬帶信號時更是如此,原因是低頻率時抑制比高,但高頻率時抑制比自然會降低。因此,模擬電源應保持干凈,并且使用時應正確去耦合電容。

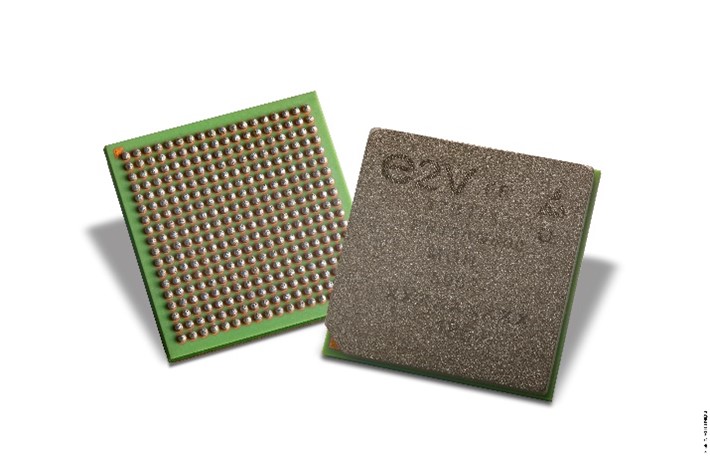

通過在系統芯片設計中選用Synopsys數據轉換器IP,設計師將經過優化的數據轉換器IP集成在系統芯片中,滿足應用要求和應對系統芯片的惡劣環境。

除了選擇IP外,IP物理集成部署不正確會影響系統性能。采用本文中的技術有助于系統地解決IP集成挑戰。除提供高質量、可靠耐用的數據轉換器IP進行系統芯片集成外,Synopsys可在集成過程中提供廣泛的工程支持(包括詳細的集成指南、集成檢查清單和由經驗豐富的新思科技應用工程師專門進行集成審核)并簡化系統芯片集成過程,有助確保芯片一次成功。

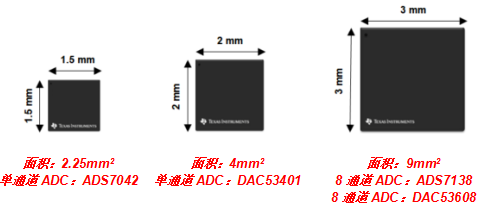

Synopsys具有超過十五年的數據轉換IP研發與應用經驗,可提供全面的、經硅驗證的200多種DesignWare數據轉換器IP產品,包括過采樣sigma delta模擬-數據轉換器、流水線型模擬-數字轉換器、逐次逼近型模擬-數字轉換器(SAR ADC)和電流舵數字-模擬轉換器。DesignWare數據轉換器IP產品具有非常低的功率損耗,占用面積小,支持從180納米到28納米的制程。

評論