PSoC 5LP:帶CPLD的可靠ARM嵌入式處理器

您是不是需要復雜可編程邏輯器件(CPLD)但又不愿放棄固件?或者說您希望最好在單個芯片中同時集成微控制器和CPLD?PSoC® 5LP是賽普拉斯半導體公司的最新片上可編程系統,當它用作CPU時,它就是一款32位的67 MHz ARM Cortex-M3處理器,而用作CPLD時,其可編程邏輯提供的基于LUT的FPGA門,相當于20,000多個門。

本文引用地址:http://www.j9360.com/article/184727.htm高效數字架構

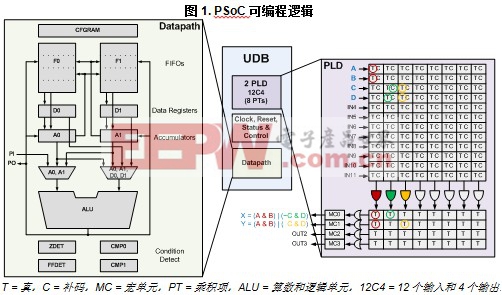

PSoC 5LP(此后簡稱為“PSoC”)以通用數字模塊(UDB)形式提供面積效率極高的可編程邏輯(如圖1所示)。UDB包含2個PLD、1個控制邏輯和1條帶有數據邏輯單元的(ALU)的數據路徑,每個模塊都是獨立而互聯的。這種架構說明,任何數字功能都是由結構化邏輯(理想適用于數據路徑)和隨機邏輯(理想適用于PLD)組合實現的。

· PLD模塊是把12個輸入饋送給到8個乘積項的陣列,其輸出提供給功能齊全的宏單元。

· 狀態和控制邏輯提供UDB和CPU之間的無縫接口。

· 數據路徑是PSoC的重要組成部分,這是一個針對通信和控制操作(如SPI或PWM所需要的)優化的8狀態微微處理器。比較某些常見功能的UDB資源使用和傳統CPLD/FPGA資源使用情況,保守估計每條數據路徑的等效門為700多個。

· 無限互聯:靈活路由對CPLD至關重要,UDB正好可實現這一點。UDB子模塊可鏈接或路由到外設,特別是UDB的任何信號輸出都能路由到任何GPIO。可能的路由組合極其豐富。

一個PSoC有多達24個UDB,因此有大量的可編程邏輯可供您使用。舉例來說,您可讓PSoC UDB支持24個8位PWM或8個簡單UART,同時仍能支持更多邏輯。當然,UDB具有可重配置這一事實特性可讓您根據自己的需求正確配置數字功能的類型和數量。

選擇模式

PSoC的主要組件就是PSoC CreatorTM,這是一款免費的集成設計環境(IDE),能幫助您按照自己所想的方式開展設計。

任何數字設計都遵循如圖2所示的步驟,一步步完成從要求到產品的過程。一旦明確了項目要求,就能在PSoC Creator中完成所有其它設計工作。

1. 基于組件的設計:如果您是一名固件工程師,在數字設計方面是新手,那么PSoC Creator能幫助您用熟悉的面向對象設計的方法創建出強大的數字設計。您可以將預先構建的、經過測試的“虛擬芯片”或組件拖放到設計中,創建SPI Master接口或開關去除抖動器再簡單不過。此外,您還可采用經預先測試的穩健可靠的API通過C語言代碼控制這些組件。一旦完成設計,PSoC Creator就能在PSoC上進行優化構建和編程。

2. 基于Verilog的設計:如果您更適應Verilog等硬件描述語言(HDL)的CPLD傳統設計,那么PSoC Creator也能滿足您的需求。您可編寫全新的Verilog代碼,將現有設計移植到PSoC UDB中,也可在設計中實例化預先構建的PSoC組件。一旦完成設計,就可讓PSoC Creator進行綜合,讓項目對應于硬件,此外也可手動操作綜合器。

萬用表相關文章:萬用表怎么用

c語言相關文章:c語言教程

評論