一種低壓高線性CMOS模擬乘法器設計

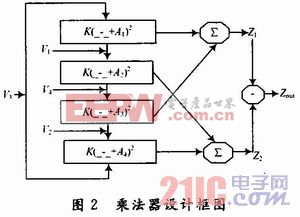

摘要:提出了一種新穎的CMOS四象限模擬乘法器電路,該乘法器基于交叉耦合平方電路結構,并采用減法電路來實現。它采用0.18μm CMOS工藝,使用HSPICE軟件仿真。仿真結果顯示,該乘法器電路在1.8 V的電源電壓下工作時,靜態功耗可低至80μW,其線性輸入范圍達到0.3 V,-3 dB帶寬可達到1 GHz,而且與先前低電壓乘法器電路相比,在同樣的功耗和電源電壓下,具有更好的線性度。

關鍵詞:CMOS模擬乘法器;低壓;高線性;減法電路

四象限模擬乘法器是模擬信號處理系統中的重要組成單元,它被廣泛地應用于鎖相環、頻率變換、調制與解調、自適應濾波等許多模擬信號處理電路中。目前,適應于低壓工作的CMOS四象限模擬乘法器由6個級聯的兩輸入組合結構單元(Combiner)組成,這種結構已廣泛應用于射頻電路中,它的NMOS管分別對源漏相接,且通過負載電阻R直接到電源。因它的輸入電壓可直接控制晶體管電流,因而該乘法器工作所需要的電源電壓很小,其最小的電源電壓是NMOS柵源電壓與負載電阻上的壓降之和。但是這種乘法器結構含有較多的電流支路,電阻也相對較多,一定程度上增加了版圖的面積和功耗,最重要的是該結構對MOS管的匹配有嚴格要求,否則線性度很難保證,這樣也就對制造工藝提出了較高的要求。針對這一缺點,本文提出了一種新型模擬乘法器結構,它采用減法電路來提高電路的線性度。

1 電路工作原理

1.1 設計思路

圖1給出適應于低壓工作的CMOS四象限模擬乘法器結構(Cornbiner)。它的輸出電壓為:

輸出電壓:

這樣最終就實現了乘法運算功能。

評論