FIR結構IQ串行處理RRC濾波器

2.2 串行處理濾波器結構

其后采用FIR結構實現RRC濾波器,其中數據輸入端使用IQ路串行輸入,即上一節中的串行數據。由于奇數階M=65FIR濾波器的時域特性,其沖擊響應滿足如下條件:

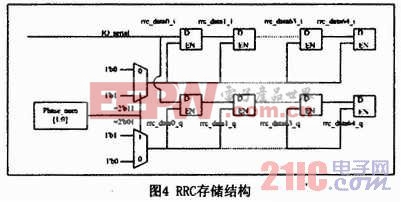

因此對于不同部分的存儲單元可以使用相同的加法單元,在下面的復用乘加器中可以設計復用結構。這里描述FIR數據存儲的結構,其中由計數器Phase_num控制數據在濾波器存儲單元中的流動。高位為1時存儲I路數據,高位為0時存儲Q路數據。數據存儲單元無法復用,因為這是濾波必需的。但是乘加器則可以通過如下小節中描述的方式復用。本文引用地址:http://www.j9360.com/article/179110.htm

2.3 復用乘加器結構

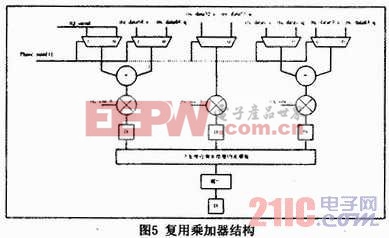

同樣,依靠計數器控制,我們可以復用同一套乘加資源,但是存儲單元依然和使用兩套FIR結構相同,這也體現了ASIC設計的本質。從圖5中我們就可以發現乘加器的輸入也由同一個計數器控制,計數器高位為1時,計算I路數據濾波結果,計數器高位為0時,計算Q路濾波結果,隨后經過兩級觸發器緩存,在輸出端形成串行IQ路數據,如此結構就節省了兩套FIR濾波器中的乘法器與加法器的結構,當FIR階數較高時就有效地節省了資源,但是這是有前提的,即射頻部分在下變頻時并沒有殘留太大的頻偏,也就是說當基帶信號并不是很理想時,或者有一個帶通信號對其進行干擾時,IQ路RRC濾波器是不一樣的,那么此時濾波系數就是不同的,則不可避免地需要兩套RRC結構。

3 結論

本文通過改變通常FIR處理結構,有效地節省了資源,只使用了一套乘加器,一套FIR濾波器結構,就完成了兩套FIR濾波器的功能,雖然數據存儲單元與兩套FIR相比并未減少,但是有效地減少了乘加資源的使用,提高了運算效率,節省了ASIC芯片的面積。當RRC濾波器階數

較高時,效果更為明顯。

評論