微處理器的電源管理方案

隨著領先微處理器的每一代后續產品對電流的需求不斷提高,為了使功耗保持在可管理的水平,就需要把工作電壓降至更低。同時,這些高電流水平帶來極大的電流變化率(di/dt),因而使電壓調節(即穩壓)也變得更加困難得多。了為緩解這一問題,穩壓容差指標一直在不斷下降。5年前,±250mV還是可接受的;到2005年,任何微處理器供電電源的最大穩壓容差將不得超過±25mV。

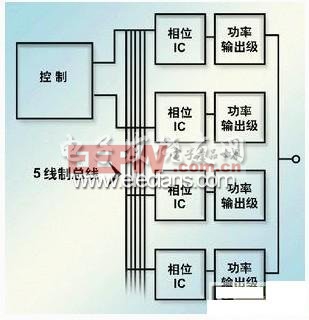

本文引用地址:http://www.j9360.com/article/178619.htm展望2005年的先進微處理器,預計未來電源供電解決方案的電流水平將從目前的60A增至130A,同時電壓將下降到1.1V。這已帶來夠大的挑戰,但更苛刻的要求將接踵而來,即如何在滿足800A/usdi/dt的條件下,實現±25mV的穩壓。更多的相位將在多相、點負載(point-load)型轉換器中被采用,而頻率將從目前的500kHz不斷增加至2005年的2MHz。此外,保持目前每安培成本水平的壓力會一直存在。從整體來看,微處理器為DC/DC轉換器設計帶來的挑戰包含了許多技術、涉及許多領域內的專門知識。為取得成功,廠商必須擁有達到基準水平的功率硅片功能;其次,封裝方案絕對要是一流的;另外,有創意的控制IC方案必不可少。最后還必須采用一個先進的電源架構將所有這些整合到一起。

功率硅片

在功率硅片領域,為了滿足未來幾年微處理器將提出的預期要求,像國際整流器公司(IR)等電源管理行業的主導廠商已經取得了長足的進步。

圖1所示的是開關品質因數(FOM),這是評判降壓拓撲結構中控制場效應管(FET)或稱高端(high-side)FET性能的一個典型方法。通過從1至2微米平面拓撲結構變為為亞微米溝道,開關品質因數被提高了1-3倍多。圖2所示的是同步或稱低端(low-side)FET的品質因數。在這里,實際上是傳導損耗主宰了處在導通電阻時域的品質因數。僅在過去的兩年中,通過將1至2微米溝道技術升級為深亞微米水平,就使品質因數提高了約3倍,今后還有更多的改進余地。

為滿足未來幾年內微處理器的需求,業界需沿著這條改進之路繼續前行。對控制FET來說,通過轉向更細的線路和橫向(lateral)拓撲結構,品質因數可獲得另一次3倍的提升。在同步FET領域,在硅溝道技術中采用越來越細的線路幾何結構還可再次獲得2.5倍的提升。在更遠的將來,為了與雄心勃勃的發展規劃同步,業界將需要采用諸如金剛砂和氮化鎵這樣的替代材料。否則,功率半導體器件的進步將不足以滿足未來微處理器的要求。

創新的封裝

在某些方面,封裝本身已成為取得進步的障礙,如SO-8的例子。該封裝是迄今為止用于面向微處理器的點負載轉換器的最流行封裝形式。SO-8帶有1.5毫歐的封裝阻抗(DFPR),能被裝入其中的硅片其阻抗要小于該封裝阻抗。SO-8還在熱阻方面表現欠佳,向下至PCB板、向上到空氣散熱(18℃/瓦)兩個方向均是如此。

為了解決這些問題,一些新型封裝已被開發出來,如IR公司的PowerPak,以改善DFPR和熱阻問題。可解決這些問題的其它封裝方面進展也層出不窮,例如:銅帶(copperstrap)、LFPak以及無底座SO-8等。盡管如此,業界還必須開發其它一些新穎的封裝方法以進一步改進熱阻性能。其中一種前景看好的新型封裝技術是將熱量向上推,然后將其釋放到電路板上方的空氣中,而不是將熱量向下壓進已在吸收若干其它元件發熱的PCB板。為將硅片所占面積和阻抗降至最低,這種新型的DIRectFET封裝采用一個銅“頂帽”,以便與上下雙向熱通道建立起機械強度很高的連接,從而極大地改善了DFPR和兩個方向上的熱阻問題。該設計有效地使板上功率密度得到雙倍地增加。

評論