CMOS工藝多功能數字芯片的輸出緩沖電路設計

摘要:為了提高數字集成電路芯片的驅動能力,采用優化比例因子的等比緩沖器鏈方法,通過Hspice軟件仿真和版圖設計測試,提出了一種基于CSMC 2P2M 0.6μm CMOS工藝的輸出緩沖電路設計方案。本文完成了系統的電原理圖設計和版圖設計,整體電路采用Hspice和CSMC 2P2M的0.6μm CMOS工藝的工藝庫(06mixddct02v24)仿真,基于CSMC 2P2M 0.6μm CMOS工藝完成版圖設計,并在一款多功能數字芯片上使用,版圖面積為1 mm×1 mm,并參與MPW(多項目晶圓)計劃流片,流片測試結果表明,在輸出負載很大時,本設計能提供足夠的驅動電流,同時延遲時間短、并占用版圖面積小。

關鍵詞:CMOS工藝;輸出緩沖電路;版圖設計;MPW計劃;在片測試

近年來,CMOS集成電路產業高速發展,在各種消費類電子、家電和汽車產品中越來越多應用到CMOS芯片,但是在電子產品系統的設計過程中,隨著CMOS工藝尺寸越來越小,單位面積上集成的晶體管越來越多,極大地降低了芯片的成本,提高了芯片的運算速度。但是,隨著工藝的進步和尺寸的減小、芯片集成度的提高、多芯片模塊的出現和數據寬度的增加,芯片外部接口上、模塊內芯片間的接口和芯片內的總線與時鐘樹的大電容驅動問題問題變得日益嚴峻,同時,它還隨著日益顯著的互聯線RLC效應而變得越來越復雜。這個問題引起了緩沖器插入技術和比例緩沖器的大量研究。

對于一個CMOS集成電路芯片來說,對于接到片外的最終輸出級電路,需要驅動包括壓點、封裝管殼以及印刷電路板的寄生電容,這些電容的總和可能達到幾十pF甚至上百pF。當一個電路的輸出要驅動一個很大的負載電容時,為了保證電路的工作速度,必須使輸出級能提供足夠大的驅動電流。在一定工藝條件下,要增大驅動電流必須增大MOS管的寬長比,然而輸出級MOS管的尺寸增大,又將使前一級電路的負載電容增大,使前一級的延遲時間加長。因此,在驅動很大的負載電容時(不僅針對連接片外的輸出級,也包括扇出很大的電路,如時鐘發生器電路等),需要一個設計合理的輸出緩沖器,緩沖器要能提供所需要的驅動電流,同時又要使緩沖器的總延遲時間最小。在CMOS集成電路中,一般是用多級反相器構成的反相器鏈做輸出緩沖器。這就是緩沖器插入技術和比例緩沖器的設計問題。

筆者首先介紹等比緩沖器的設計原理,最后基于CSMC2P2M 0.6μm CMOS工藝,針對各種緩沖器鏈的速度和面積優化情況,提出了一種優化的輸出緩沖電路的設計,并應用在一款多功能數字芯片上參與MPW計劃流片。仿真和流片測試表明,本設計的輸出緩沖電路具有占用面積小、功耗低傳輸延遲小等優點。

1 等比緩沖器鏈的設計

1.1 設計原理和優化比例因子

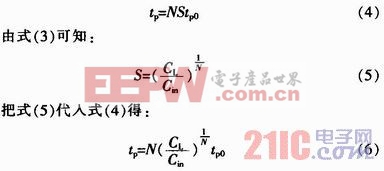

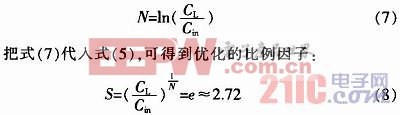

比例緩沖器的兩種基本類型是等比和變比緩沖器。Lin在文獻中第一次提出了等比緩沖器,其各級反相器與第一級的大小成式(1)中的比例關系。Jaeger在進一步的研究中得出了經典的等比因子,其他一些研究者進一步在最優等比因子中考慮了分開的柵漏電容負載和短路等效電容。Vemurut討論了變比緩沖器,其各級的比例關系如式(2)所示。

![]()

所謂等比緩沖器鏈,就是使反相器鏈逐級增大相同的比例,這樣每級反相器有近似相同的延遲時間,對減小緩沖器的總延遲時間有利。模擬表明,當反相器輸入波形的上升、下降時間與輸出波形的上升下降時間基本相等時,反相器的充放電電流為一個三角形波形,電流的峰值就是MOS管的最大飽和電流。如果輸入波形的上升、下降時間比輸出波形的大,則電流峰值下降,也就是說這種情況下沒有發揮出MOS管的最大驅動能力。如果輸入波形的上升、下降時間比輸出波形的小,則充放電電流波形從三角形變為梯形,這說明充放電時間加長。

考慮一個逐級增大的S倍的反相器鏈,如圖1所示。

以第一級反相器尺寸為單位1,則第二級反相器中NMOS和PMOS的寬度都比第一級增大S倍,第三級比第一級增大S2倍,如此類推,第N級反相器比第一級增大SN-1倍。

如果忽略連線寄生電容和各個節點的PN結電容。則圖1的反相器鏈中有:

![]()

這里把C1看作依次增大尺寸的第N+1級反相器的輸入電容,因此有:

![]()

如果一個反相器驅動一個和它相同的反相器的延遲時間為tp0,則上述反相器鏈中每級的延遲時間均為Stp0,則總的延遲時間tp為:

如果知道了tp0和Cin以及最終要驅動的負載電容CL,則可以找到一個合適的N值,使輸出緩沖器總的延遲時間tp最小。可以得到:

這就是說,如果要使尺寸較小的電路(Cin很小)驅動一個很大的負載電容CL,必須通過一個緩沖器,理想情況下,緩沖器由N級逐級增大e倍的反相器鏈組成,這樣可以使總延遲時間最小。

評論