用于工業(yè)信號(hào)電平的精密24位、250 kSPS單電源Σ-Δ型ADC系統(tǒng)

連接/參考器件

本文引用地址:http://www.j9360.com/article/175523.htmAD7176-2 24位、250 kSPS Σ-Δ型ADC,建立時(shí)間20 μs

AD8475 精密、可選增益、全差分漏斗放大器

ADR445 5 V超低噪聲LDO XFET基準(zhǔn)電壓源

評(píng)估和設(shè)計(jì)支持

電路評(píng)估板

AD7176-2電路評(píng)估板(EVAL-AD7176-2SDZ)

系統(tǒng)演示平臺(tái)(EVAL-SDP-CB1Z)

設(shè)計(jì)和集成文件

原理圖、布局文件、物料清單

電路功能與優(yōu)勢(shì)

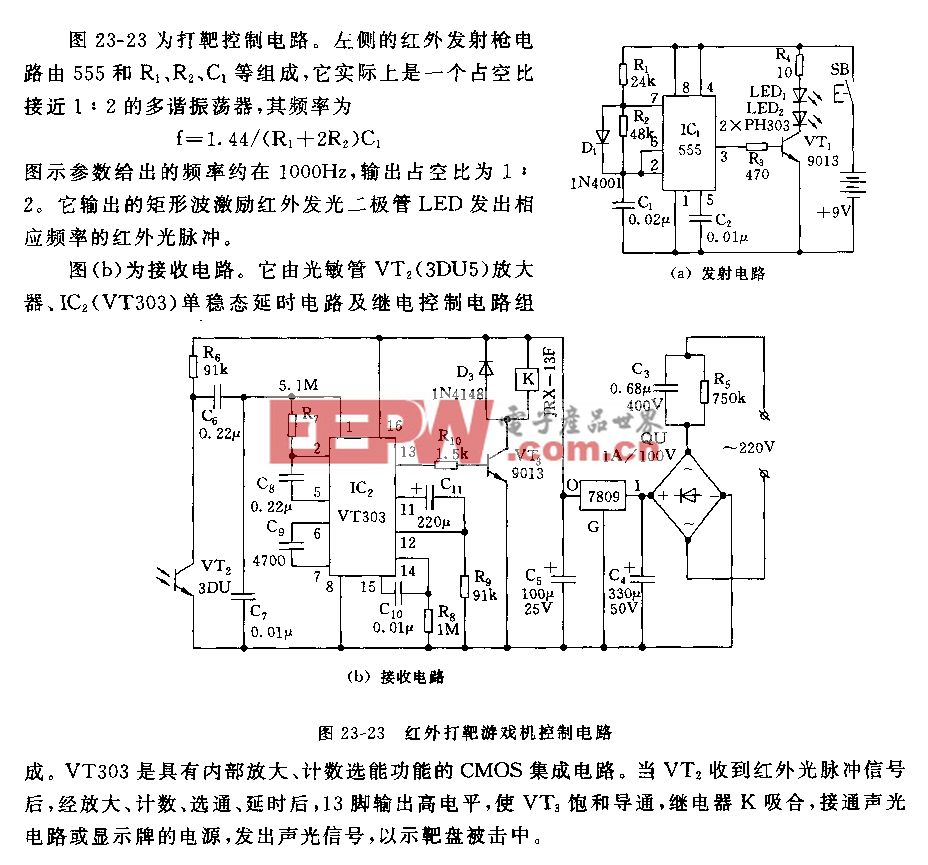

對(duì)工業(yè)電平信號(hào)進(jìn)行采樣時(shí),必須提供快速高分辨率轉(zhuǎn)換信息。通常,當(dāng)采樣速率達(dá)到500 kSPS時(shí),模數(shù)轉(zhuǎn)換器(ADC)具有的最高分辨率為14位至18位。圖1所示電路是一款單電源系統(tǒng),針對(duì)工業(yè)電平信號(hào)采樣進(jìn)行優(yōu)化,集成一個(gè)24位、250 kSPS Σ-Δ型ADC。兩個(gè)差分通道或四個(gè)偽差分通道中的每一個(gè)都能夠以17.2位無(wú)噪聲代碼分辨率、最高50 kSPS的速率對(duì)其進(jìn)行掃描。

本電路利用創(chuàng)新型差分放大器和內(nèi)置激光調(diào)整電阻執(zhí)行衰減和電平轉(zhuǎn)換,通過(guò)具有低電源電壓的精密ADC可以解決獲取±5 V、±10 V和0 V至10 V的標(biāo)準(zhǔn)工業(yè)電平信號(hào)并進(jìn)行數(shù)字化處理的問(wèn)題。本電路的應(yīng)用包括過(guò)程控制(PLC/DCS模塊)、醫(yī)療以及科學(xué)多通道儀器和色譜儀。

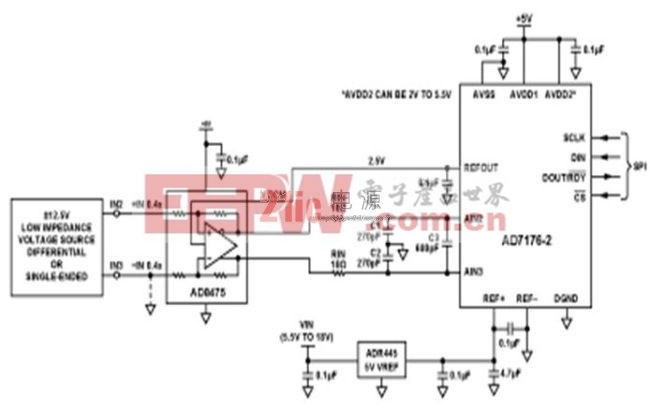

圖1. 工業(yè)信號(hào)用高精度、24位ADC驅(qū)動(dòng)器(原理示意圖:未顯示所有連接和去耦)

電路描述

工業(yè)電平信號(hào)施加于AD8475精密差分漏斗放大器上,該器件可將輸入信號(hào)衰減0.8倍或0.4倍。它集成經(jīng)過(guò)調(diào)整并匹配的精密電阻,用來(lái)控制衰減。當(dāng)AD8475使用5 V單電源并且增益設(shè)置為0.4時(shí),此電阻支持最高±12.5 V的單端或差分輸入。器件提供最高±15 V的輸入過(guò)壓保護(hù)。

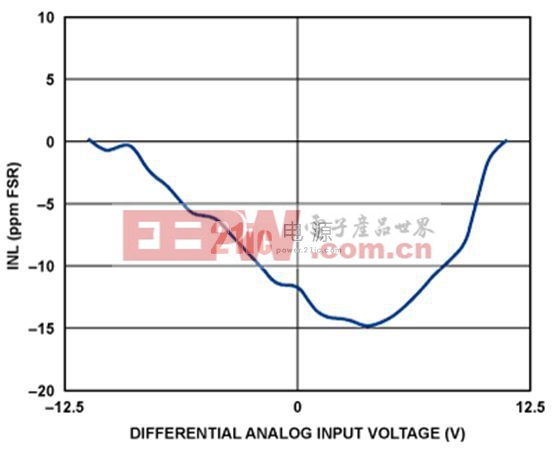

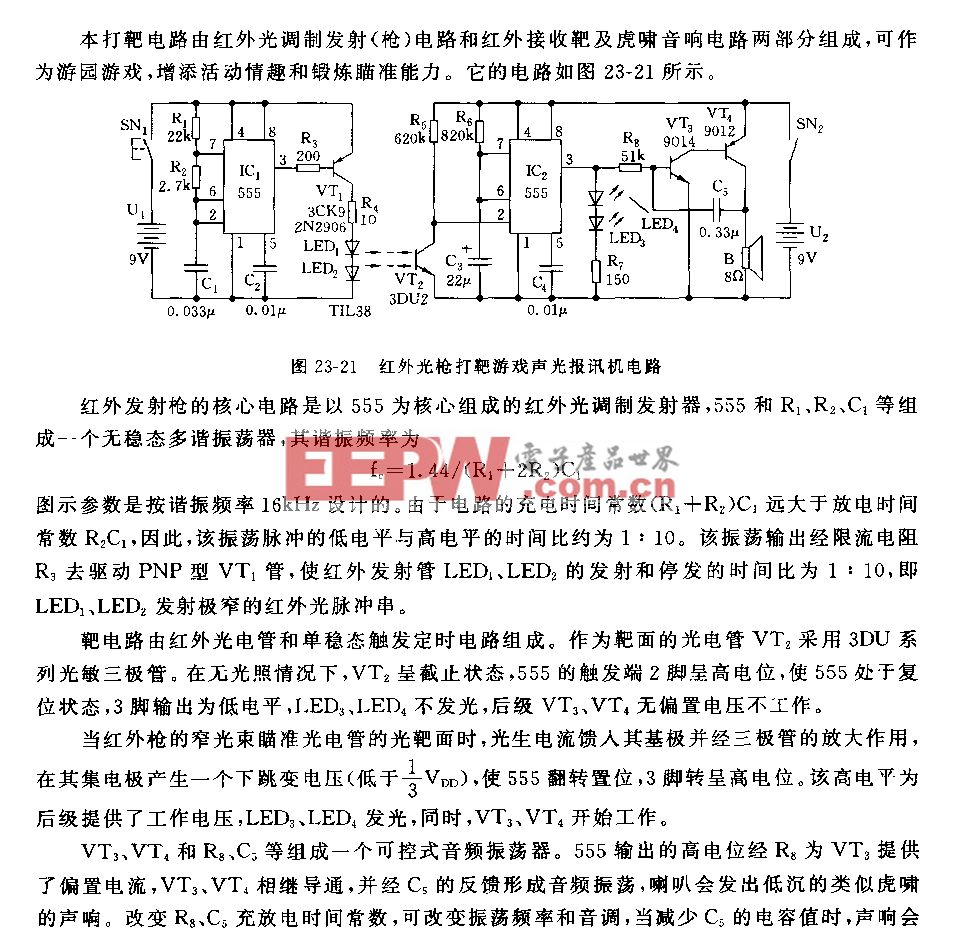

當(dāng)輸入信號(hào)(增益為0.4)處于±10 V單端或差分輸入范圍內(nèi)時(shí),AD8475和AD7176-2器件組合能夠保持線性度,如圖4中的測(cè)量INL限值所示;圖中,測(cè)量端點(diǎn)分別為?10 V和+10 V。此時(shí),AD8475的輸出擺幅介于0.5 V和4.5 V之間。

通過(guò)對(duì)VOCM引腳施加所需的共模電壓,便可設(shè)置共模輸出。圖1所示電路中,通過(guò)將AD7176-2 ADC的2.5 V REFOUT電壓施加于AD8475的VOCM引腳,完成共模電壓的設(shè)置。

AD8475提供衰減和電平轉(zhuǎn)換,以便驅(qū)動(dòng)AD7176-2的采樣電容輸入;功耗僅為3.2 mA。

AD8475放大器的輸出連接到RC濾波器網(wǎng)絡(luò),可提供差分和共模噪聲濾波以及AD7176-2輸入采樣電容所需的動(dòng)態(tài)充電。該網(wǎng)絡(luò)還可隔離放大器輸出,使其不受動(dòng)態(tài)開(kāi)關(guān)電容輸入的反沖影響。共模帶寬(RIN、C1)為59 MHz。差模帶寬(2 × RIN、0.5C1 + C3)為9.8 MHz

還可設(shè)置AD8475,使其接受單端信號(hào)。將-IN 0.4×輸入接地,并對(duì)+IN 0.4×輸入施加單端信號(hào)。

AD7176-2 24位、Σ-Δ ADC對(duì)AD8475的輸出進(jìn)行采樣,并轉(zhuǎn)換為數(shù)字輸出。轉(zhuǎn)換速率和數(shù)字濾波器特性可針對(duì)5 SPS至250 kSPS的輸出數(shù)據(jù)速率進(jìn)行調(diào)節(jié)。

AD7176-2可配置為兩個(gè)全差分輸入或四個(gè)偽差分輸入。ADC支持最高50 kSPS的通道掃描速率。AD7176-2的無(wú)噪聲位性能為17.2位(250 kSPS);20.8位(1 kSPS);以及21.7位(50 SPS)。

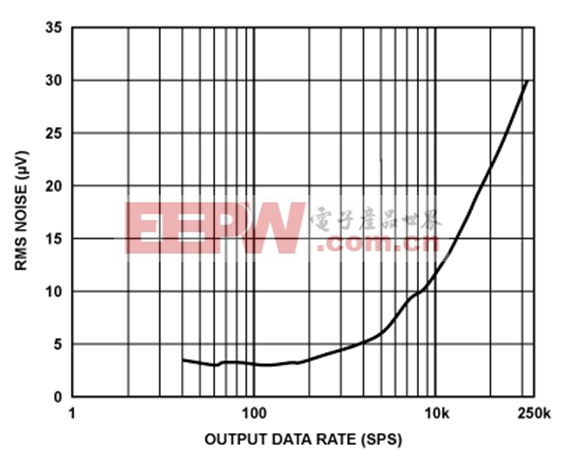

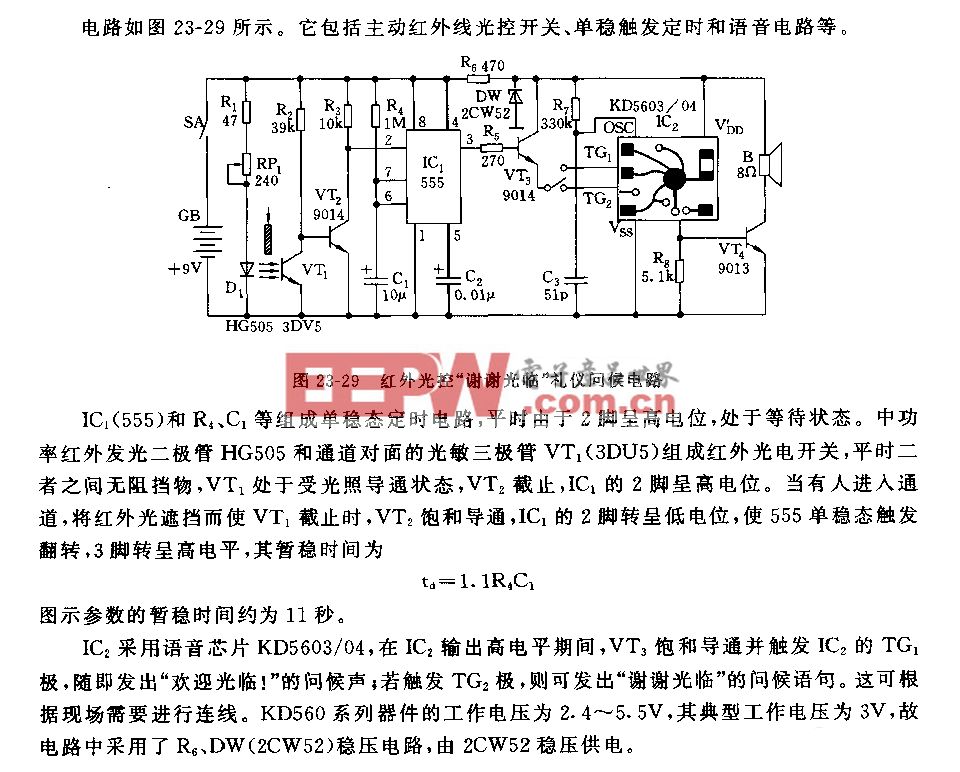

圖2表示輸入接地時(shí)的總系統(tǒng)有效均方根噪聲。數(shù)據(jù)速率為250 kSPS時(shí),有效均方根噪聲約為30 μV rms。請(qǐng)注意,滿量程時(shí),本電路的線性度在±10 V輸入下達(dá)到最佳狀態(tài),計(jì)算時(shí)滿量程輸入設(shè)為20 V p-p。

圖2. 均方根輸出噪聲與輸出數(shù)據(jù)速率的關(guān)系

有效分辨率以位數(shù)表示,折合到20 V滿量程輸入范圍的計(jì)算公式為:

有效分辨率 = log2(FSR/均方根噪聲)

有效分辨率 = log2(20 V/30 μV) = 19.3位

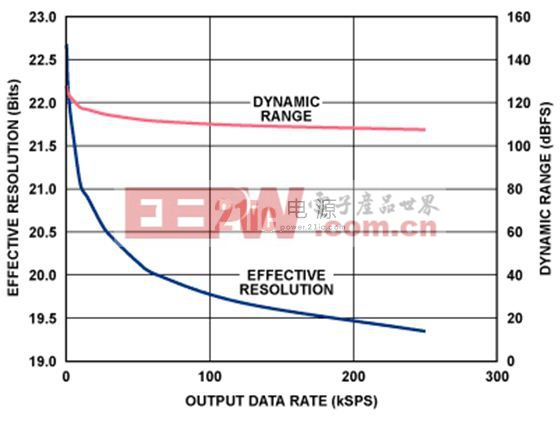

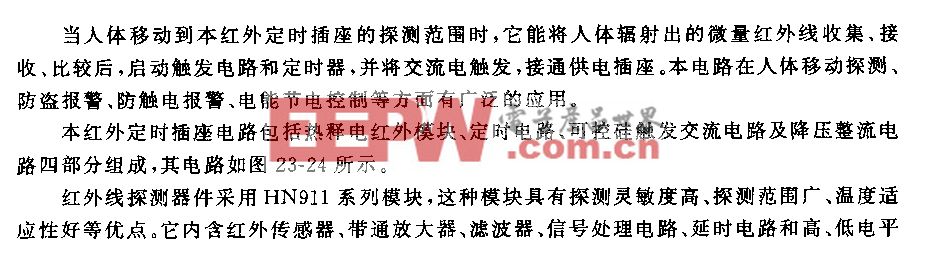

圖3. 有效分辨率(均方根位數(shù))與輸出數(shù)據(jù)速率的關(guān)系

先將均方根噪聲轉(zhuǎn)換為峰峰值噪聲近似值(均方根噪聲乘以系數(shù)6.6),有效分辨率便可轉(zhuǎn)換為無(wú)噪聲代碼分辨率。計(jì)算結(jié)果約為2.7位,隨后將其從有效分辨率中扣除,以得到無(wú)噪聲代碼分辨率。如本例所示,經(jīng)計(jì)算后,19.3位有效分辨率相當(dāng)于16.6位無(wú)噪聲代碼分辨率。這一結(jié)果與AD7176-2在無(wú)緩沖短路輸入情況下,輸出數(shù)據(jù)速率為250 kSPS時(shí)的17.2位無(wú)噪聲位規(guī)格相比,大約有0.3位的差異。這是由于本例僅采用±10 V作為滿量程范圍,而非±12.5 V的最大值。

圖4顯示采用端點(diǎn)法獲得的系統(tǒng)積分非線性,用滿量程(FSR)的ppm表示。

圖4. 積分非線性(INL,以FSR的ppm表示)與輸入電壓的關(guān)系

評(píng)論