基于DSP/BIOS的FIR數字濾波器設計與實現

數字信號處理器(DSP)擁有強大的數字信號處理能力,與其配套的集成可視化開發環境CCS(Coder Composer Stu-dio)更方便了 DSP應用程序的開發。DSP/BIOS是CCS的重要組成部分,它實質上是一種基于DSP平臺的規模可控的實時操作系統內核。這里主要研究在DSP上利用DSP,BIOS實現FIR數字濾波器的方法。

2 TMS320F2812及DSP/BIOS內核介紹

TMS320F2812是基于TMS320C2XXX內核的定點數字信號處理器,具有數字信號處理及強大的事件管理和嵌入式控制功能,適于有大批量數據處理的控制系統。其性能可用于數字濾波器設計。

TMS320F2812采用高性能的靜態CMOS技術,時鐘頻率達150 MHz;低功耗(內核電壓1.9 V,I/O口電壓3.3 V);采用哈佛總線結構,片上集成許多片上外設,可實現更多功能。開發環境是集成開發環境CCS,支持C/C++/匯編嵌入式實時操作系統DSP/BIOS,JTAG調試接口。

DSP/BIOS內核是一個尺寸可伸縮的實時內核,它是為實時信號處理應用而設計的,主要包括:(1)DSP/BIOS配置工具。該工具可用來創建和配置在應用程序中使用的DSP/BIOS內核對象,也可使用該工具配置存儲器,線程優先權以及中斷處理;(2)DSP/BIOS實時分析工具。CCS中的分析丁具使用戶可測試和分析目標DSP上應用程序的運行,包括監測CPU負荷、日志、線程執行情況等;(3)DSP/BIOS API函數。用戶在PC端采用C、C++或匯編語言編寫調用DSP/BIOS API函數的應用程序;(4)器件支持庫。提供許多宏和函數,用來簡化片上外設的配置和管理。

3 數字濾波器分析

數字濾波器根據沖激響應持續時間可分為有限沖激響應濾波器(FIR)和無限沖激響應濾波器(IIR)。其中FIR濾波器能夠保證嚴格的線性相位特性,且不存在穩定性問題。窗函數法和頻率采樣法等是設計FIR數字濾波器的常用方法。窗函數法在時域中進行,其原理簡單,易于實現,但存在在相同設計指標下濾波器的階數通常會偏大的問題。頻率采樣法對于只有少數幾個非零值采樣的窄帶選頻濾波器較有效。這里分析如何在DSK2812板上利用CCS本身所帶的操作系統實現一種通過窗函數法實現的FIR濾波器。FIR濾波器的各項指標可以通過現有的表查找,其設計步驟如下:

(1)給定所要求的理想頻率響應函數Hd(ejw);(2)對理想頻率響應函數進行反傅里葉變換,則得到系統單位脈沖響應為:hd(n)=IDFTFT[Hd(ejw)];(3)根據過渡帶及阻帶衰減最小的要求查表,可選定窗ω(n)的形狀及除數,N的大小,一般N的值要做幾次試探才能最終確定;(4)得到所設計的FIR濾波器的單位抽樣響應(該響應逼近理想):h(n)=hd(n)ω(n),n=0,1…,N-1;(5)求H(ejw)=DTFT[h(n)],檢查是否滿足設計要求,若不滿足,則需重新按照上述步驟設計。

4 數字濾波器的實現

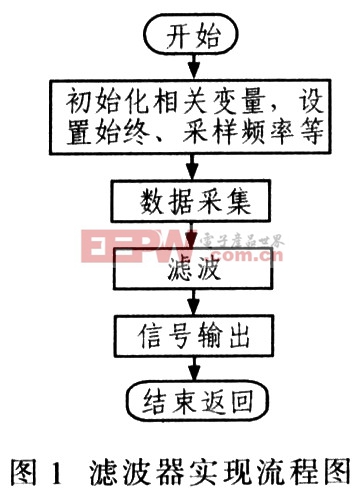

要實現的低通FIR濾波器:通帶邊緣頻率ωp=10 kHz,阻帶邊緣頻率ωs=22 kHz,阻帶衰減δ2=75 dB,采樣頻率fs=50 kHz。根據對濾波器的分析可求得系統的差分方程。所求得的h(n)在程序設計過程中可用一個數組存放。X(n)是A/D轉換器采樣值。讓其逐項相加,再輸出即可。實現濾波器所采用的硬件平臺為DSK2812,實現流程如圖1所示。

|

評論