基于超薄外延技術的雙擴散新型D-RESURF LDMOS設計

摘要:文中針對高壓節能應用領域,開發了一種基于超薄外延技術的雙擴散BCD兼容工藝,實現了一種新型D-RESURF結構的700V LDMOS設計。結構中N型外延的厚度減小為4.5μm,漂移區長度縮減至70μm,使得芯片面積和制造成本大幅減小。并通過仿真設計,優化了器件結構的表面電場分布,使反向擊穿電壓達到700V的同時,使器件導通電阻降為33Ω·mm2。流片結果表明,功率管可以達到設計要求。

關鍵詞:超薄外延;D-RESURF;雙阱高壓LDMOS;VLD

0 引言

SPIC(Smart Power IC)目前已經被廣泛應用于開關電源、電機驅動、工業控制、汽車電子、日常照明、家用電器等領域。在SPIC中,通常需要將耐高壓的功率器件與低壓控制電路集成在同一芯片上。在高壓功率器件應用領域中,LDMOS由于工作電流密度大、導通電阻低、開關特性好等優點而被廣泛采用。從工藝應用角度看,LDMOS擁有橫向結構的優勢,可采用BCD工藝條件將LDMOS、CMOS和BJT器件單片集成在同一硅片上。在LDMOS設計過程中,新技術的應用決定了器件的耐壓和導通電阻特性。在本文中,LDMOS成熟地在結構中引入了D-RESURF技術,D-RESURF技術是在N型漂移區表面引入P型降場層形成節終端擴展區,可使表面電場得到改善,同時增加了器件反向擊穿電壓;另外D-RESURF技術也使漂移區單位面積可注入雜質密度增大,從而降低了器件的導通電阻。

目前,高耐壓的LDMOS一般采用厚度為10μm左右的外延層,其外延厚度遠高于目前標準CMOS工藝,并且用于高壓集成時需要增加對通隔離的時間,因而不易與標準CMOS工藝兼容。為了解決上述問題,本文采用了P埋層的薄外延完善該LDMOS結構,以傳統CMOS工藝,在厚度為4.5μm的超薄外延層上,仿真設計了耐壓為700V以上的LDMOS器件。

1 器件結構與分析

本文中所采用的雙擴散高功率的BCD工藝涉及了多種類型器件,主要包括耐壓為700V的高壓LDMOS、耐壓為40V的中壓MOS管、5.8V低壓CMOS器件、二極管、電阻等。因此在設計LDMOS的過程中需要考慮與其他器件在工藝加工過程、注入濃度、版次等方面的匹配性。

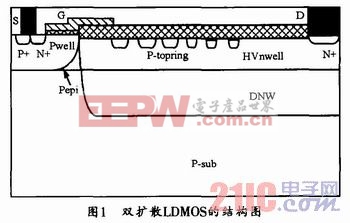

新型雙擴散LDMOS的設計要求是:在4.5μm超薄外延層工藝條件下,可以滿足700V以上高耐壓要求,同時盡可能的降低導通電阻;在此基礎上壓縮漂移區長度,優化器件的結構尺寸,達到減小芯片版圖面積和制造成本的目的。雙擴散LDMOS的結構如圖1所示,多環P型降場層P-topring被分為數個隔離的島,用以改善器件的表面電場;圖中的P-sub表示工藝中采用P型襯底材料;LDMOS的耐壓漂移區分為上下兩部分:

HVnwel表示N型外延層漂移區部分,DNW表示器件襯底漂移區部分;Pwell表示LDMOS的體區,用來形成MOS器件的溝道。LDMOS的柵板位于體區上方,它的右側延伸了一段到場氧上,形成場板,用來改善器件表面電場分布。

1.1 器件表面降場層的結構描述

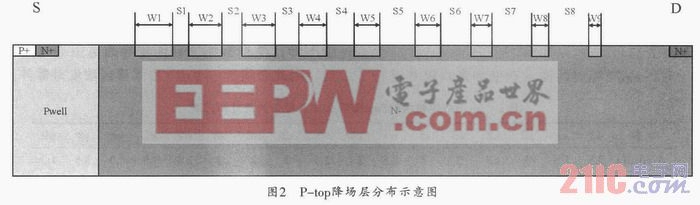

在器件表面降場層的設計中采用了DRESURF技術,在器件的源漏端之間的N型漂移區表面引入了相反導電類型的多個P-top環形摻雜區。這些環形降場層的設計是基于橫向變摻雜(VLD)技術,VLD技術是通過改變雜質注入窗口的尺寸和間距,有效地控制P-top降場層在器件表面的濃度分布。在P型雜質以相同的注入濃度注入后,雜質通過不同間距和尺寸的窗口進入漂移區表面,在相同的環境溫度下產生橫向和縱向擴散,最終在器件表面的降場層濃度分布近似線性,從漏端到源端濃度的線性增加,可以使表面電場的分布均勻。P-top降場層被分為九個不同間隔的區域,如圖2所示,P-top從左到右各環的橫向尺寸Wn在逐漸變大,而環間距Sn則逐漸變小,實現從左到右(從漏到源)P-top降場層濃度的近似線性分布。

在這些P-top區域的P型雜質是以高能量,高濃度的方式注入,這樣可以確保器件HNV漂移區保持較高的雜質濃度來耗盡P-top反型區,在漂移區外延層內,如此高的積分電荷器件確保了器件擁有較低的導通電阻。

評論