基于超薄外延技術的雙擴散新型D-RESURF LDMOS設計

2.2 漂移區濃度對擊穿電壓和導通電阻的影晌

當漏端電位從零開始增加到220V左右時,體內PN節耗盡區隨著電壓的增加而擴展,直到整個漂移區完全耗盡(此時體內PN節的峰值電場遠遠小于擊穿電場的最小值),電壓繼續增大過程中,器件表面的P-top、N-結與器件體內的N-、P-sub結的電場峰值在隨之上升,在N型漂移區總的注入劑量不變的情況下,HNV注入劑量的增加會使LDMOS表面電場的擊穿點的由漏端向P-top的源端方向轉移。表現為HNV注入劑量為1.1E 12cm-2~1.35E12cm-2時,N型漂移區濃度偏低,LDMOS的漂移區會在較低的漏源電壓下全部耗盡,電場在漏區集中,導致器件首先在漏區/N型漂移區處擊穿;N型漂移區表面雜質濃度的增加會使P-top完全耗盡的同時、表面電場的分布更加均勻,導通電阻趨于下降。當HNV注入繼續上升時,N型漂移區濃度偏高時,LDMOS的漂移區無法完全耗盡,電場在P-top降場層靠源區一側集中,器件同樣會過早擊穿。于此同時DNW的注入濃度在逐步下降,使得整體漂移區比導通電阻會逐漸增加。因此必須折中考慮N型漂移區濃度對器件擊穿電壓和比導通電阻的影響。

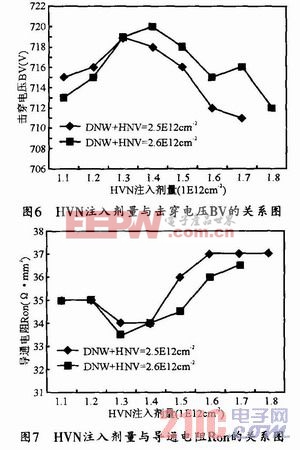

TSUPREM4和MEDICI模擬仿真漂移區濃度分布,當漂移區總注入劑量在2.4E12cm-2~2.7E12cm-2范圍內,HNV保持注入劑量在1.1E12cm-2~1.8E12cm-2變化時,器件擊穿電壓大于700V。考慮到工藝誤差等因素,選取漂移區總注入劑量分別為2.5E12cm-2和2.6E12cm-2,HNV注入劑量由1.1E12cm-2~1.8E12cm-2變化時,觀察分析擊穿電壓BV與導通電阻Ron變化情況如圖6、7所示。本文引用地址:http://www.j9360.com/article/166181.htm

觀察HVN注入劑量與擊穿電壓BV和導通電阻Ron的關系圖,當HNV注入劑量由1.1E12cm-2增加時,器件表面濃度得到改善,使擊穿電壓上升,同時導通電阻也在相應減小,隨著濃度的增加,器件漂移區濃度分布趨于最優化。當HNV注入劑量超過1.5E12cm-2繼續增加時,漂移區表面濃度過剩,器件此時擊穿發生降場層附近。表現為擊穿電壓逐漸降低,與此同時,漂移區DNW的注入隨著HNV的增加而逐漸降低,器件漂移區上下濃度分布失衡,導致器件的導通電阻增大。因此,流片時選取HNV注入劑量為1.3E12cm-2~1.5E12cm-2時,DNW注入劑量為1.1E12 cm-2~1.3E12cm-2。此時對應仿真結果導通電阻小于35Ω·cm2,擊穿電壓BV大于714V。

3 結束語

本文對一種基于超薄外延技術的雙阱LDMOS進行設計研究,該新型器件采用了D-RESURF,橫向變摻雜(VLD),雙阱注入漂移區等技術。通

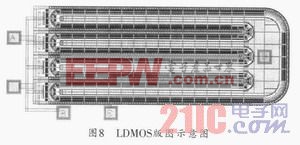

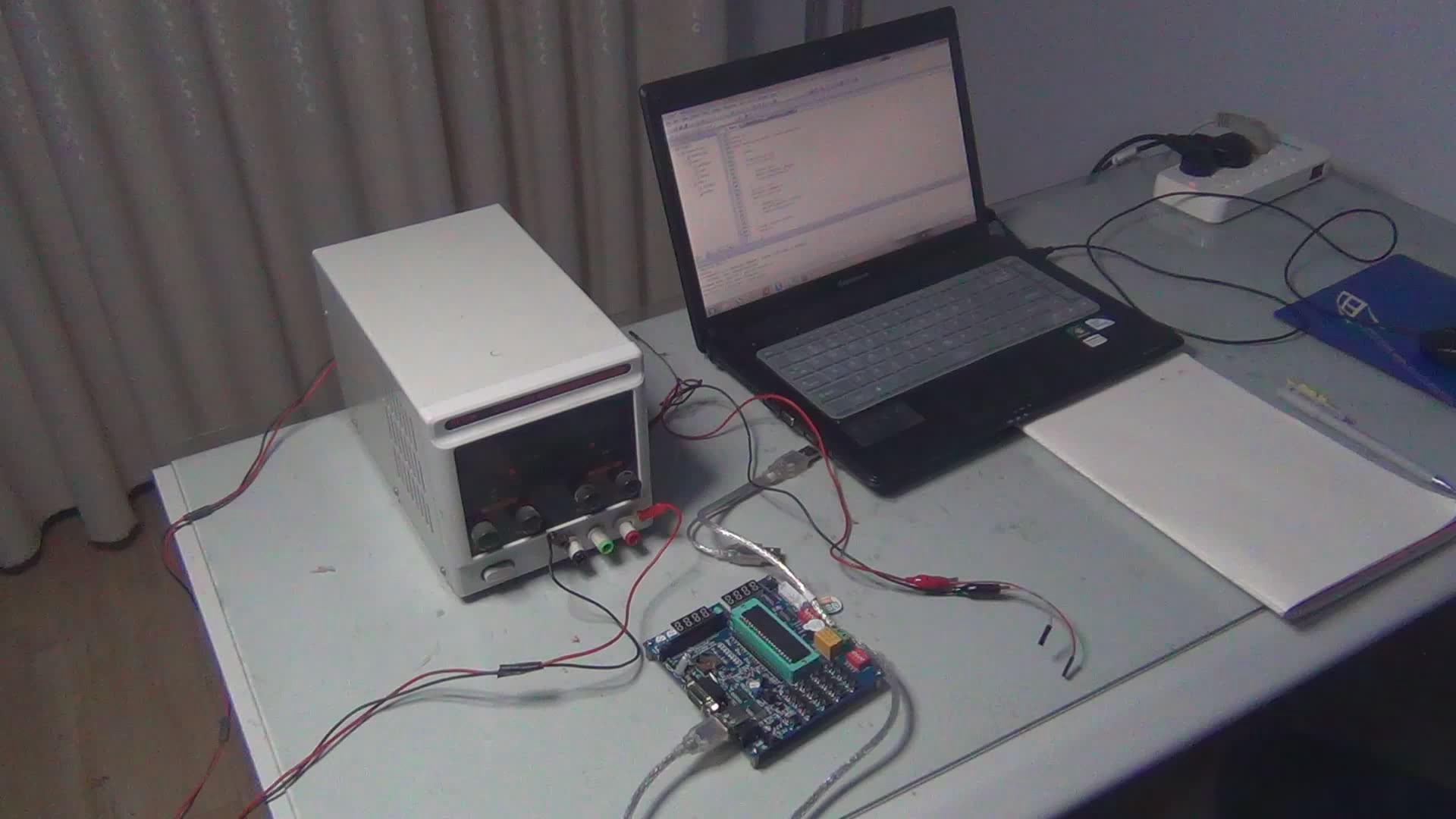

過對漂移區表面降場層的幾何尺寸和注入濃度的仿真優化,改善了器件表面電場的耐壓特性,同時在漂移區總注入劑量不變的情況下,研究了HNV注入濃度與擊穿電壓與導通電阻的關系,分析研究仿真結果,得出最佳濃度分布。根據這些仿真設計結果,對該型LDMOS進行投片驗證,其器件版圖如圖8所示。當P-top注入劑量為2.5E13cm-3,HNV注入劑量為1.3E12cm-2。DNW注入劑量為1.3E12cm-2時,測試器件結果表明LDMOS擊穿電壓可以達到690V,結果接近設計要求,實現了與中、低壓器件的良好工藝兼容。

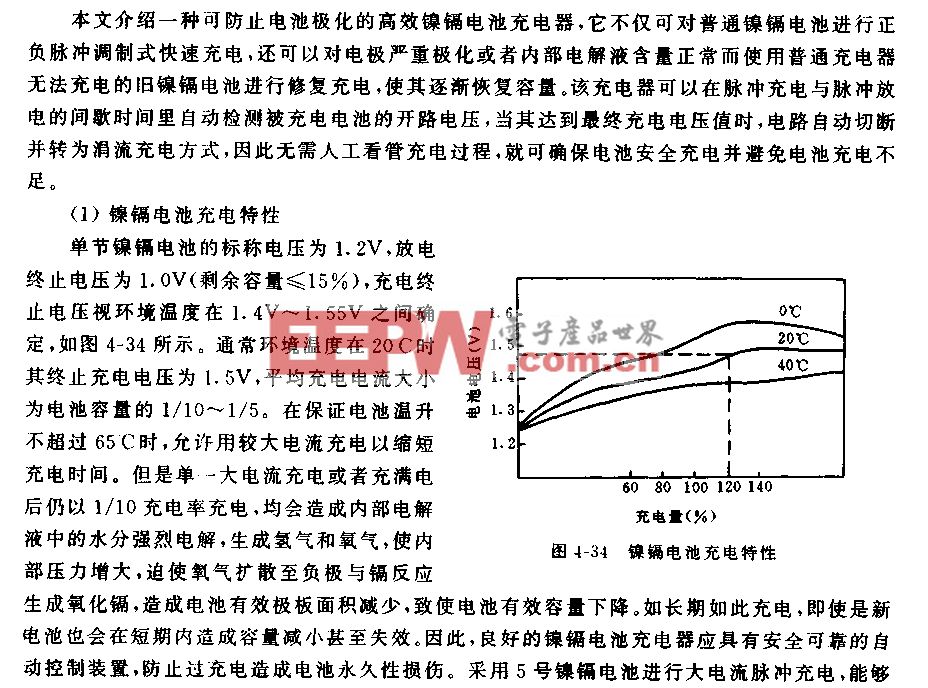

評論