基于超薄外延技術的雙擴散新型D-RESURF LDMOS設計

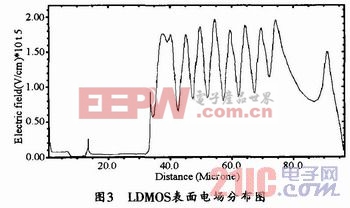

在用MEDICI、Tsuprem4軟件對該器件進行工藝器件聯合仿真時,觀察結果如LDMOS表面電場分布圖中所示,漂移區內由高濃度P-top環引起的電場波峰均勻地分布在漂移區電場中部,各電場波峰值大小相似,約為2×1015V/cm。在該分布狀況下,器件源漏間漂移區的表面電場的耐壓分布得到有效地改善。本文引用地址:http://www.j9360.com/article/166181.htm

1.2 器件漂移區的結構分布

N型漂移區的濃度分布和尺寸結構,決定著LDMOS電場分布和比導通電阻的大小。為實現與中、低壓MOS良好的工藝兼容,器件漂移區的形成采用了雙阱雙次注入的設計方法,通過對外延層和襯底表面分別注入不同劑量N型雜質來實現。在外延生長前,在襯底表面注入P型材料形成漂移區的DNW部分;生長4.5μm薄外延后,在DNW正上方的超薄外延中實現第二次注入擴散,完成漂移區的HNV部分。雙注入不但成功地在4.5μm超薄外延的基礎上使漂移區結深達到10μm,同時由于漂移區的截面積大幅增加,也可以在橫向上大幅縮短了漂移區長度。

在仿真設計過程中,由于P-top降場層的大劑量注入,允許漂移區的HNV區域保持較高的濃度分布,器件比導通電阻隨之降低。由于DNW雜質在外延生長加熱過程中會向上反擴,增大外延層的濃度,所以DNW區域的注入濃度要小于HNV。為防止過早發生體內擊穿,DNW在外延生長前需要較長時間的高溫加熱,使得注入結深向襯底擴散,確保器件在襯底縱向保持6μm漂移區結深。兩次不同劑量,不同加熱環境的注入,實現了器件電場分布的優化設計,有效地滿足了器件在不同區域的技術需求。

評論