25G高速無源通道的設計挑戰

OIF CEI-11G LR和10G Base KR規范已發布了好幾年。隨著100Gbps標準的不斷演進,出于互連密度和功耗的考慮,單通道的速率也逐漸從10Gbps演變為更高的速率。比如OIF CEI-25G LR就試圖將單通道的速率從11Gbps提高到25Gbps,與此同時,將功耗限制在前一版本的1.5倍以內。雖然CEI-25G LR并未被正式發布,但一些最基本的通道參數卻已在草案中被基本確定下來。在SerDes廠商和無源通道廠商的不懈推動下,10Gbps+的速率被不斷地刷新。一些半導體廠商先后推出了15Gbps、20Gbps的SerDes,Avago公司更是在今年的DesignCon上展示了符合CEI-25 LR草案的背板驅動器和高達30Gbps的SerDes。

本文引用地址:http://www.j9360.com/article/155904.htm雖然25Gbps背板規范并未被發布,相關的SerDes也還未量產,但光通信廠商早就開始了40Gbps DQPSK的應用,將PCB上單一通道的速率推進到20Gbps。背板方面,雖然國內廠商只能拿到15Gbps的SerDes,但毫無疑問,不用多久,20Gbps以上的SerDes也會被開放。因此,本文將試圖對25Gbps無源通道設計時遇到的挑戰(尤其是在信號完整性方面)進行分析和探討。

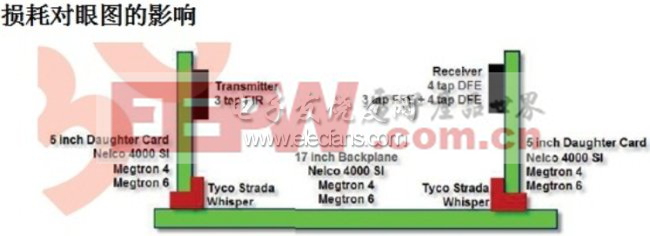

一個完整的25Gbps鏈路的構成通常如圖1所示。

圖1:25Gbps完整鏈路示意,TP1~TP4為測試點。

25Gbps鏈路也是一個典型的點對點拓撲,發射端和接收端均做了信號處理,即我們通常所說的均衡。一般發射端被稱為加重,接收端被稱為均衡。其中發射端的加重又分為預加重和去加重;接收端的均衡又分為模擬均衡和數字均衡,分別為CTLE和DFE。發射端和接收端的均衡通常被用來補償數據在有損鏈路中傳輸時的損耗,以便在接收端獲得張開的眼圖以及符合規范的BER。25G無源通道主要被用于芯片間(chip-chip),芯片與模塊間(chip-module)或者背板的應用中。在信號完整性方面遇到的挑戰主要包括傳輸損耗、反射和串擾。

對抗傳輸損耗

無源通道就像一個低通濾波器,總是會降低傳輸信號的幅度。信號在通過連接器、PCB走線、過孔、IC引腳和線纜等無源鏈路中的每一部分時,總會造成幅度上的損失和抖動的累積。當信號到達接收端時,眼圖通常已經閉合(圖2、圖3)。作為鏈路的設計者,通常需要設法降低傳輸過程中的損耗,這也被稱為插損。以背板為例,25Gbps無源通道的損耗主要由高速連接器、過孔和走線造成。

評論