基于DSP和FPGA的磁浮列車同步485通信方式的研究

0 引言

本文引用地址:http://www.j9360.com/article/152490.htm在高速磁浮交通系統中,車載測速定位單元對車輛的位置和速度進行實時測量,并將位置和速度信號通過無線電系統傳送至地面上的牽引控制系統和運行控制系統,以用于長定子直線同步電機牽引的反饋控制及車輛運行的指揮和安全防護。測速定位單元是牽引和運控系統閉環控制的核心和關鍵。

測速定位單元緊鄰懸浮電磁鐵及長定子繞組和鐵心,處于懸浮磁場和牽引磁場中,電磁環境非常復雜,對其通信設備的電磁兼容性能提出了很高的要求。另外,為滿足牽引控制系統的需求,測速定位信號的精度要求相當高。因此,對測速定位信號傳輸的速度、實時性及可靠性都有非常高的要求。

1 同步485的實現方法

考慮到測速定位單元的工作環境及通信功能需求,在選擇其與車載無線電系統之間的通信方式時,經過分析和比較,決定采用傳輸速率較高的同步通信方式,并使用屏蔽性能較好的雙絞線實現RS-485平衡型差分傳輸。

1.1 接口設計及通信協議

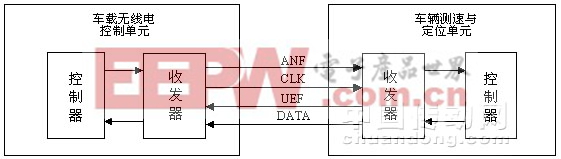

測速定位單元與車載無線電控制單元之間的通信接口關系如圖1所示。車載無線電控制單元為主控方,車輛測速與定位單元為受控方。通信雙方均由收發器和控制器構成,收發器之間采用RS-485同步串行接口方式,每個接口有4對差分線。

圖1 通信接口關系示意圖

圖1中,CLK為時鐘信號,ANF為無線電請求信號,UEF為門控信號,DATA為數據信號。車輛測速定位單元每20ms向無線電控制單元發送一次數據,傳輸速率為512kbps。為了防止信號干擾的小脈沖,ANF信號的寬度為10個CLK信號;在ANF信號變為低信號后,等待10個CLK信號寬度后,UEF才開始跳變為有效。ANF、UEF、DATA信號均在CLK的上升沿變化,在無信號傳輸時,UEF、DATA、ANF均為低電平,時鐘信號保持傳輸。數據傳輸時,采用左移方式,即先傳高位,后傳低位。信息幀格式如表1所示:

表1 信息幀格式

1.2 同步485的收發器實現

在本文所論述的通信系統中,在車輛測速定位單元及車載無線電控制單元雙方均采用Xilinx公司的XC2S100作為通信的收發器,模擬同步485的發送與接收時序。同步485的FPGA設計主要是基于Verilog 硬件描述語言,所使用的EDA工具包括ISE(含其內部集成工具)、Modelsim。

(1)時鐘及定時信號的的產生:

對于車載無線電控制單元需要產生512k速率的時鐘信號與20ms一次的ANF(無線電請求)信號。另外,對于該單元在串行接收定位數據時其接收時鐘應為512k(波特率時鐘)的16倍,即8M。因此,分頻器在同步485通信方式中得到廣泛應用。

1) 偶數分頻較為簡單,只需設計一個計數器進行計數,待計數至分頻數的二分之一時使分頻后的時鐘電平翻轉即可;奇數分頻較為復雜,因為計數器不能對非整數進行計數,需使用一定的算法進行處理。對奇數分頻模塊進行功能仿真后的波形如圖2所示:

圖2 分頻模塊仿真波形

評論