基于LabVIEW和ARM嵌入式數據采集與遠程傳輸控制系統

2.2 ADC6620設計

AD6620的任務是將高速數據流變成當前可實時處理的中低速數據流。在本設計中,AD6620數據輸入端代表指數含義的3位(EXP0~EXP2)接地,且工作在單輸入通道模式下(A/B=3.3 V),以模式0接收來自于ARM的配置信息(MODE=GND),采用并行方式輸出數據(PAR/SER=3.3 V)。

2.3 其它設計

本設計所采用的ARM開發板是由廣州友善之臂公司所生產的QQ2440V3,其上有一個44針的系統總線接口,它與FPGA連接起來完成數據與控制信息的傳輸。FPGA與SRAM的設計比較簡單,這里不再贅述。本文引用地址:http://www.j9360.com/article/152253.htm

3 數據采集系統的軟件設計

為完成系統任務,需要實現幾個方面的軟件設計:

a)正交數字下變頻器AD6620濾波器以及控制寄存器設計。

b)在FPGA上實現系統控制、SRAM讀寫地址生成、數據通道選擇等功能的Verilog HDL程序。

c)ARM上基于嵌入式Linux操作系統的數據采集硬件驅動程序。

d)ARM上客戶端應用程序。

e)遠程主機上基于LabVIEW的服務器以及顯示、頻譜分析、存儲與回放程序。

3.1 AD6620濾波器及控制寄存器設計

AD公司專門針對AD6620芯片推出了濾波器設計軟件fltrdsn以及監視控制軟件AD6620,但該軟件是基于計算機并口與AD6620芯片連接的,不適應設計中遠程數據傳輸與控制、多客戶端的任務要求。可以利用該軟件將設計成功的濾波器以及配置文件保存下來,利用LabVIEW的文件處理功能自動將信息提取出來,通過網絡遠程配置AD6620。

3.2 FPGA邏輯設計

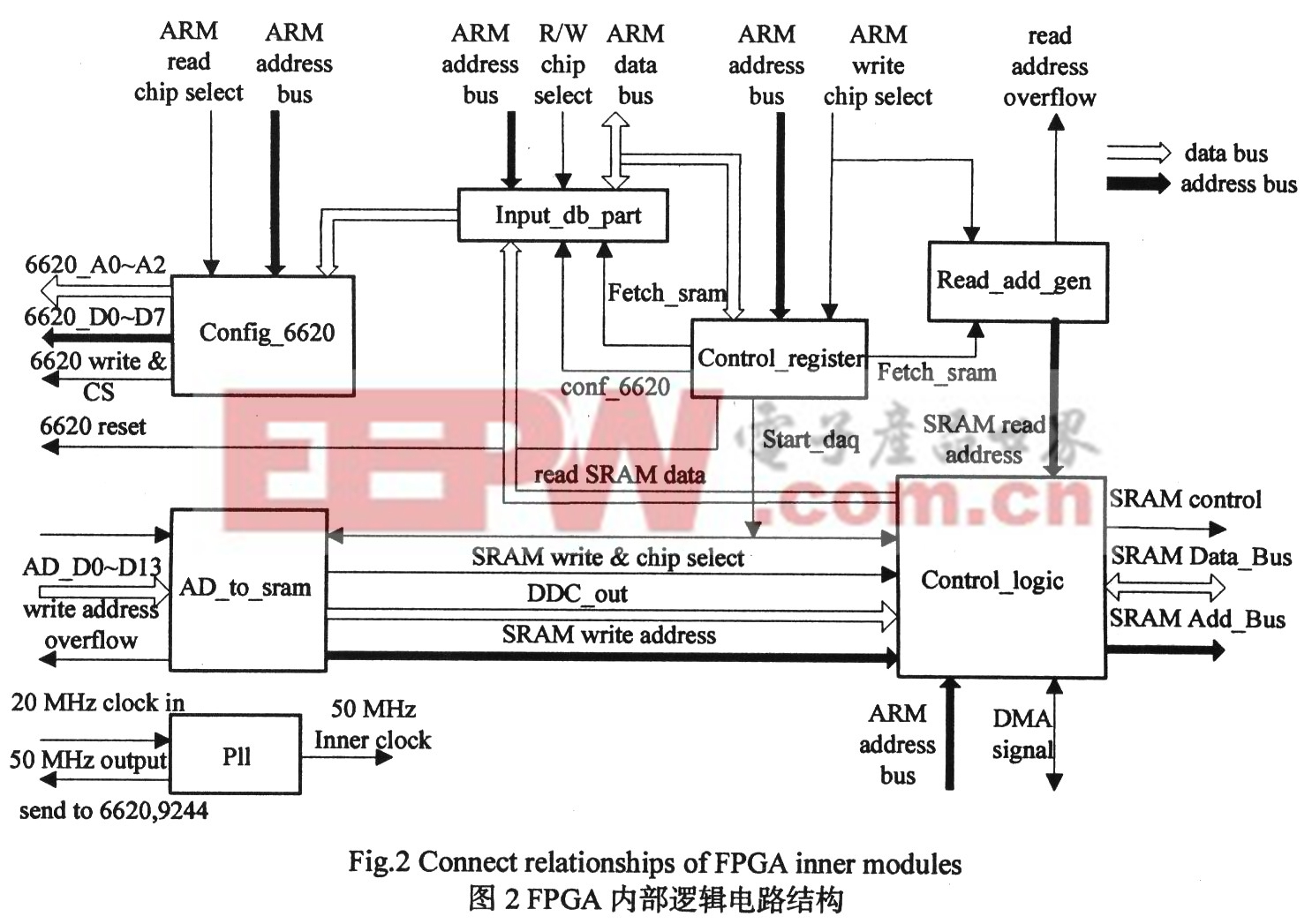

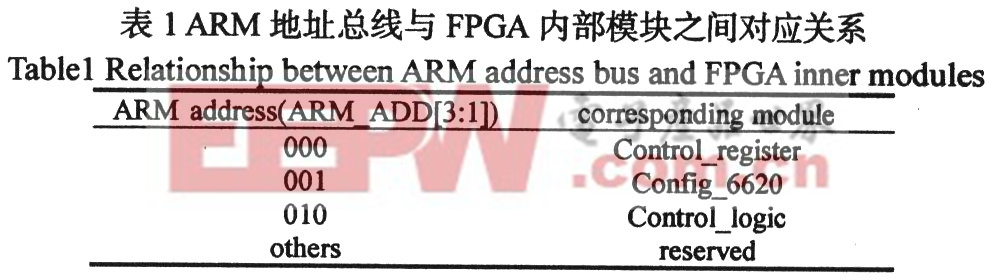

FPGA內部邏輯電路結構見圖2。考慮到后續設計的需要,FPGA內部使用ARM地址總線的低3位來選擇當前操作的模塊,具體的地址與內部模塊對應關系見表1。

圖2中各模塊功能進一步說明如下:

a)Input_db_part:雙向數據總線分離。配合由Control_register送來的控制信號,在Conf_6620有效時將數據總線上的數據送至Config_6620模塊,完成AD6620配置,在Fetch_sram信號有效時將讀SRAM得到的數據傳送至ARM數據總線。

評論