基于ARM平臺的嵌入式軟件保護方案

需要注意的是目前使用的很多嵌入式系統都是基于沒有特別設計安全機制的硬件平臺。本文以原ARM處理器平臺為例,通過增加1塊安全協處理器,就可以實現低成本、有實效的安全保護,并且能夠抵御兩類比較寬泛的攻擊:一類是在系統的啟動過程中的攻擊,如果系統啟動過程中沒有安全保護措施,很可能被非法用戶使用非授權的軟件。另一類是外部存儲器及總線攻擊,當程序代碼保存在外部非易失存儲器上時,可以輕易被黑客拷貝。另外,片外存儲器與片上系統(SoC)之間的總線傳輸也容易受到攻擊。

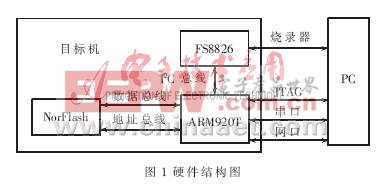

1 硬件結構

本方案的硬件結構如圖1所示。處理器平臺采用三星公司的S3C2442,內核為ARM920T,外置1塊2 MB的NorFlash用以存放密文數據,ARM通過總線方式對NorFlash進行訪問,該硬件結構中最重要的部分是添加了1塊安全協處理器:福華公司的嵌入式系統軟件保護芯片FS8826。該芯片可通過I2C或SPI總線與SOC連接,這里使用I2C方式。PC機能夠對硬件平臺中的每個芯片進行編程控制:通過JTAG端口、串口及網口與ARM進行通信,通過專門的燒錄器對FS8826的硬件密鑰和安全存儲區進行寫入。

2 軟件實現

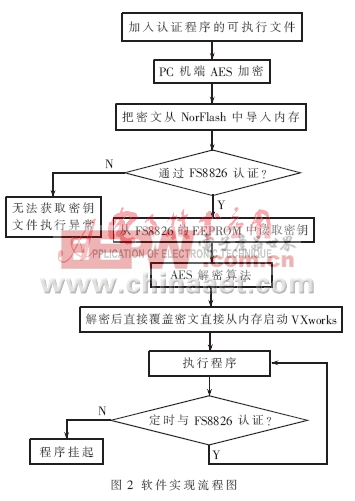

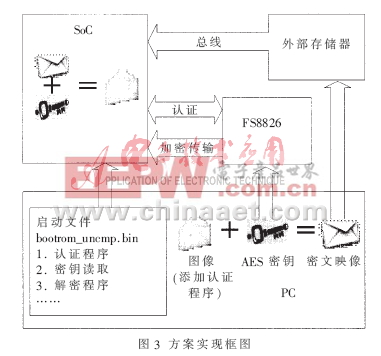

軟件設計從兩個主要方面考慮,一是代碼加密,二是版權認證。前者主要通過AES(Advanced Encryptiong Standard)加解密算法實現,其算法密鑰的管理以及版權認證將依靠FS8826來實現,最終達到安全啟動嵌入式操作系統以及保護運行時的版權目的。安全啟動方案基于Bootloader+Image的加載機制,也是ARM處理器通用的引導機制。首先采用AES加解密算法在PC機端將編譯完成Image加密,利用FS8826安全存儲區存放AES算法密鑰,密文存儲在片外存儲器中,ARM啟動時將密文加載入內存。然后在Bootloader啟動過程時加入與FS8826的認證操作,認證通過則在該過程中使用AES解密算法解密Image,并用明文將原內存中的密文覆蓋,系統正常運行中加入與FS8826的實時通信監測,確保在授權目標機上運行程序。軟件實現流程如圖2所示,相應的方案實現框圖如圖3所示。

2.1 AES算法

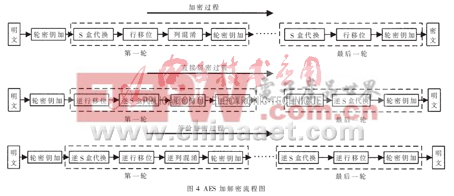

AES是美國國家標準和技術研究所(NIST)選定的高級加密標準,是目前對稱加密領域內的主流算法。其數據分組固定為128 bit,密鑰分組可支持128 bit/192 bit/256 bit。核心過程為數據塊矩陣的Nr(10/12/14)次輪操作。每一次輪操作都由S盒代換(SubBytes)、行移位(ShiftRows)、列混淆(MixColumns)和輪密鑰加(AddRoundKey)4個函數組成,第Nr次輪操作不包含MixColumns 函數。密鑰擴展為每一輪變換提供輪密鑰[2]。本方案中加密在PC機端離線完成,沒有時間和運行效率的特別要求,但是解密在ARM9處理器中完成,其運行時間將作為系統啟動的一部分,所以下面針對解密部分的算法程序結合其實現平臺進行優化設計。

直接的解密算法是將加密過程的每一步求逆并倒置次序得到,然而這樣并不利于優化。算法的創始人提出了一種等價解密過程,在解密的輪變換中交換逆行移位和逆S盒代換,輪密鑰加和逆列混淆的順序,只需要調整密鑰的編排方案即可。在實現中等價解密過程可以將解密輪變換中的前3個步驟綜合生成1張4 KB的T表用于查詢,即可快速準確地完成解密[2]。具體流程如圖4所示。

加解密過程使用電碼本模式(ECB)運行,即將消息段逐個分別加解密。實現采用移植性較好的標準C編程。針對ARM處理器的特點,C語言具有以下優化的實現方式[3]:

(1) 數據類型設置:ARM處理器內部是32 bit寄存器,如果變量長度與ARM內部寄存器長度不一致,將會使得變量的存取都需要附加其他指令[3]。AES算法中密鑰及數據都是以字節為單位運算,優化時調整為32 bit,僅在輸入輸出時進行位數變換,可以帶來很大的速度改進。

(2) 循環展開:ARM處理器中每一次循環最少有4個周期的循環開銷[3]。解密輪變換涉及4個子函數調用,循環執行Nr-1次。在等價解密算法融合了3個子函數形成T表查詢,于是可以把輪變換展開,在不增加太多代碼量的基礎上,每一個數據分組解密減少4(Nr-1)個周期。當密鑰位長、密文數據量大時節省的循環開銷就比較可觀。

評論