嵌入式系統的PCI Express時鐘分配

PCI Express (PCIe)是嵌入式和其它系統類型的背板間通信的一個非常理想的協議。然而,在嵌入式環境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結構的PCIe時鐘分配方案就變得并不理想。本文將討論如何使用一個多點信號來分配PCIe時鐘,而且仍滿足PCIe第二代規范嚴格的抖動要求。

本文引用地址:http://www.j9360.com/article/152086.htmPCIe計時

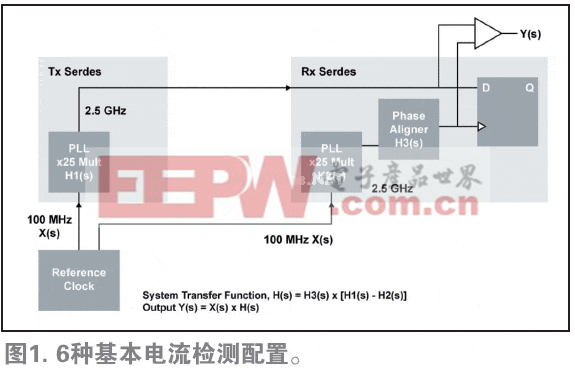

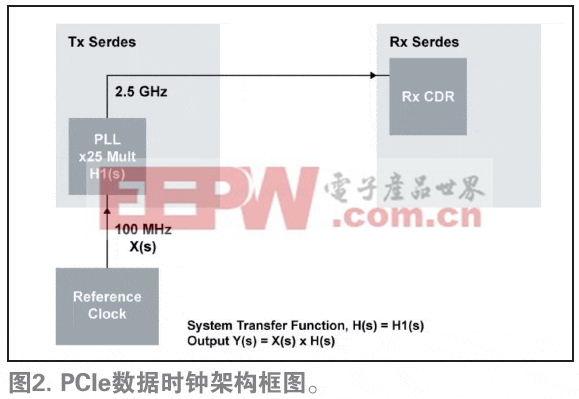

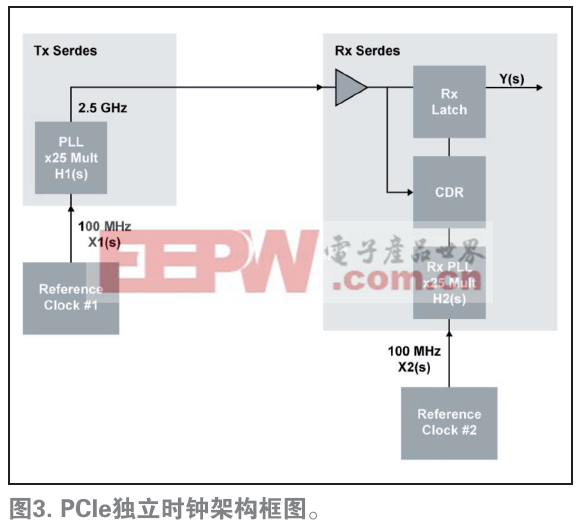

PCIe基本規范1.1和2.0為信令速率2.5Gbps和5.0Gbps的時鐘分配定義了三個不同模型,見圖1、圖2和圖3。

評論