嵌入式系統的PCI Express時鐘分配

共用時鐘架構作為最常使用的方法有很多理由。首先,大多數支持PCIe接口的商用芯片只適用于這種架構。其次,這種架構是唯一可以直接支持展頻計時(Spread Spectrum clocking,簡稱SSC)的架構。SSC在減少電磁干擾峰化方面起著非常重要的作用,因此可以簡化符合系統電磁輻射限制的工作(見圖4)。最后,這種架構最容易形成概念和設計。

共用時鐘架構最大的缺點在于需要為系統中每個PCIe端點分配基準時鐘。頻率為 100MHz或125MHz的時鐘以及PCIe規范嚴格的抖動要求使得這一架構變得尤其復雜。對2.5Gbps工作的限制為86ps――106采樣的一系列樣本的峰-峰相位抖動。而5.0Gbps工作的限制為3.1ps(均方根抖動值)。然而,要在5.0Gbps工作,收發器首先要在2.5Gbps協商,如果兩端都可以,再提高到5.0Gbps。這就是說如果系統支持任何5.0Gbps鏈接,則基準時鐘就必須同時滿足兩者的抖動指標。

獨立的數據時鐘架構不會受到上述限制,但卻大幅增加了時鐘系統設計的復雜性,且在不使用單邊帶信令時不支持SSC。

基準時鐘抖動的管理規范是PCIe基本規范1.1和2.0,而檢驗抖動達標的方法詳細列在PCIe抖動建模修訂版1.0D和PCIe抖動和BER修訂版1.0中。機電規范提供了機械尺寸信息、電信號定義和功能。其中一些,如卡機電(Card Electromechanical,簡稱CEM)1.1和CEM2.0規范也為基準時鐘、Tx鎖相環(Phase-Locked Loop,簡稱PLL)、Rx PLL和介質提供了抖動預算。嚴格來講,CEM規范只申請了PC和服務器ATX,以及基于ATX的尺寸。其它已出版的機電規范覆蓋了其它尺寸,如用于移動計算平臺的Mini Card Electromechanical Specification 1.2。

對于大多數嵌入式系統,上述這些規范可以全部或部分用來規定嵌入式系統PCIe時鐘分配方案提供指南。例如,許多CEM文件規定了對基準時鐘分配Host ClockSignal Level(HCSL)協議的使用。然而,許多嵌入式系統希望使用低電壓正射極耦合邏輯(Low Voltage Positive Emitter Coupled Logic,簡稱LVPECL)或多點低電壓差分信號(Multipoint-Low-Voltage Differential Signaling,簡稱M-LVDS)信令,以實現時鐘分配網絡更遠的距離和/或噪聲容限。

許多嵌入式系統需要在其背板之間分配包括時鐘在內的大量高速信號。為了解決這些背板上經常出現的繁重電氣負載問題,這些信號需要有非常強大的驅動器和高邊緣速率。這帶來了干擾和其它信號完整性的危險,尤其是在背板比最差設計點的負載更低時。另一個設計上的挑戰在于PCIe詳細規定了100MHz或125MHz的基準時鐘,這是一個很難在高負載長背板上順利分配的頻率。

除了PCIe規范嚴格的抖動限制和需要更長的信號距離,嵌入式系統通常還受到可能通過背板連接器和背板本身的信號量的限制。當定制系統時,確定連接器引腳排列是最關鍵的任務之一。

建議的共用時鐘分配方案

由于時鐘頻率和抖動限制,最常見的共用時鐘架構設計利用點對點差分信號對來分配基準時鐘,其中一個差分信號對將抵達系統的每個PCIe端點。如果一張卡上有多個PCIe端點,就可以從背板獲得一個基準時鐘輸入,并利用零延遲緩沖器(Zero Delay Buffers,簡稱ZDB)提供卡上時鐘分配網絡。然而,即使這樣,由于PCIe 5.0Gbps運行的抖動限制,設計起來也是非常困難的。

假設我們能設計出這樣的卡上分配方案,我們仍需要提供從PCIe主到系統上每張卡的點對點連接。在嵌入式系統中,這需要在主卡插槽上增加大量連接器引腳,并在背板上增加大量有特殊布線要求的線跡。這還要給主卡插槽插入與其它插槽截然不同的引腳排列。

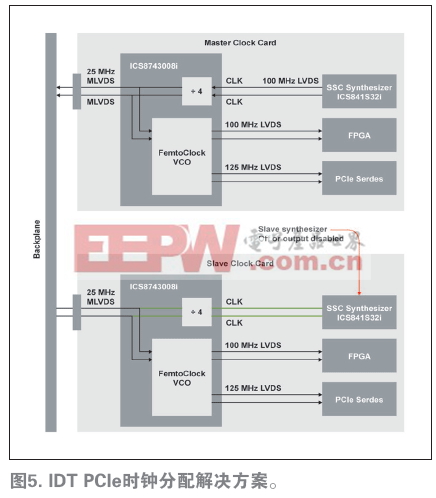

一個消除這些限制的解決辦法是降除主卡上的PCIe基準時鐘,并利用一個M-LVDS多點信號在背板之間進行分配,然后將其提高到目標卡所需的頻率。盡管理論上非常簡單,但實現PCIe抖動限制卻很棘手(見圖5,注意綠色信號線不起作用)。

這一解決方案可提供一個M-LVDS對,用來驅動或接收符合PCIe的基準時鐘。如圖5所示,在許多嵌入式系統中,根據應用的”與/或”插槽進行分配,每張卡都可作為主操作或端點操作。顯然,如圖所示,只用于其中一種模式操作的卡將被簡化。系統中的一張卡將作為主,利用其板上晶振生成滿足PCIe限制的基準時鐘。這個時鐘將利用內部時鐘分配網絡驅動所有板上PCIe器件。該時鐘也將到達非PLL除法器電路,將100MHz或125MHz向下降除為25MHz的背板頻率,然后將除降了的基準時鐘驅動到系統的其余卡上。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論