采用DSPBuilder的FIR濾波器的方案實現

1.引言

本文引用地址:http://www.j9360.com/article/152043.htm在信息信號處理過程中,如對信號的過濾、檢測、預測等,都要使用濾波器,數字濾波器是數字信號處理(DSP,DigitalSignalProcessing)中使用最廣泛的一種器件。常用的濾波器有無限長單位脈沖響應(ⅡR)濾波器和有限長單位脈沖響應(FIR)濾波器兩種[1],其中,FIR濾波器能提供理想的線性相位響應,在整個頻帶上獲得常數群時延從而得到零失真輸出信號,同時它可以采用十分簡單的算法實現,這兩個優點使FIR濾波器成為明智的設計工程師的首選,在采用VHDL或VerilogHDL等硬件描述語言設計數字濾波器時,由于程序的編寫往往不能達到良好優化而使濾波器性能表現一般。而采用調試好的IPCore需要向Altera公司購買。筆者采用了一種基于DSPBuilder的FPGA設計方法,使FIR濾波器設計較為簡單易行,并能滿足設計要求。

2 FIR濾波器介紹

2.1 FIR濾波器設計的原理

FIR濾波器的數學表達式可用差分方程(1)來表示:

其中:r是FIR的濾波器的抽頭數;b(r)是第r級抽頭數(單位脈沖響應);x(n-r)是延時r個抽頭的輸入信號。

設計濾波器的任務就是尋求一個因果,物理上可實現的系統函數H(z),使其頻率響應H(ejw)滿足所希望得到的頻域指標。

2.2 設計要求

數字濾波器實際上是一個采用有限精度算法實現的線性非時變離散系統,它的設計步驟為先根據需要確定其性能指標,設計一個系統函數H(z)逼近所需要的技術指標,最后采用有限的精度算法實現。本系統的設計指標為;設計一個16階的低通濾波器,對模擬信號的采樣頻率fs為48KHz要求信號的截止頻率fc=10.8kHz輸入序列位寬為9位(最寬位為符號位)。

3 DSPBuilder介紹

DSPbuilder是Altera推出的一個DSP開發工具,它在QuartusⅡFPGA設計環境中集成了Mathworks的Matlab和simulinkDSP開發軟件[2]。

以往Matlab工具的使用往往作為DSP算法的建模和基于純數學的仿真,其數學模型無法為硬件DSP應用系統直接產生實用程序代碼,仿真測試的結果也僅僅是基于數學算法結構。而以往FPGA所需的傳統的基于硬件描述語言(HDL)的設計由于要考慮FPGA的硬件的δ延時與VHDL的遞歸算法的銜接,以及補碼運算和乘積結果截取等問題,相當繁雜。

對DSP是Builder而言,頂層的開發工具是MatLab/Simulink整個開發流層幾乎可以在同一環境中完成,真正實現了自定向下的設計流程,包括DSP系統的建模、系統級仿真、設計模型向VHDL硬件描述語言代碼的轉換、RTL(邏輯綜合RegisterTransferLevel)級功能仿真測試、編譯適配和布局布線、時序實時仿真直至對DSP目標器件的編程配置,整個設計流程一氣呵成地將系統描述和硬件實現有機地融為一體,充分顯示了現代電子設計自動化開發的特點與優勢。

4 FIR數字濾波器的DSPBuilder設計

4.1 FIR濾波器參數選取

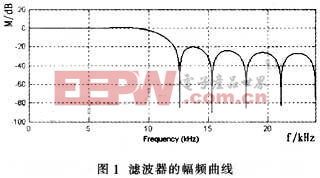

用Matlab提供的濾波器設計的專門工具箱―――FDATool仿真設計濾波器,滿足要求的FlR濾波器幅頻特性如圖1,由于浮點小數FPGA中實現比較困難,且代價太大,因而需要將濾波器的系數和輸入數據轉化為整數,其中量化后的系數在Matlab主窗口可直接轉化,對于輸入數據,可乘上一定的增益用Altbus控制位寬轉化為整數輸入。

4.2 FIR濾波器模型建立

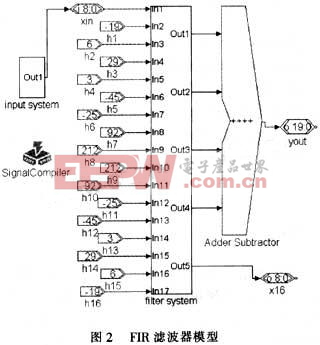

根據FIR濾波器原理,可以利用FPGA來實現FIR濾波電路,DSPBuilder設計流程的第一步是在Matlab/Simulink中進行設計輸入,即在Matlab的Simulink環境建立一個MDL模型文件,用圖形方式調用AlteraDSPBuilder和其他的Simulink庫中的圖形模塊,構成系統級或算法級設計框圖(或稱Simulink建模),如圖2所示。

評論