用FPGA+DSP實現HDLC(高級數據鏈路控制)功能

引言

本文引用地址:http://www.j9360.com/article/151586.htmHDLC的ASIC芯片使用簡易,功能針對性強,性能可靠,適合應用于特定用途的大批量產品中。但由于HDLC標準的文本較多,ASIC芯片出于專用性的目的難以通用于不同版本,缺乏應用靈活性。有的芯片公司還有自己的標準,對HDLC的CRC(循環冗余碼校驗)序列生成多項式等有不同的規定。專用于HDLC的ASIC芯片其片內數據存儲器容量有限,通常只有不多字節的FIFO(先進先出存儲器)可用。對于某些應用來說,當需要擴大數據緩存的容量時,只能對ASIC再外接存儲器或其他電路,ASIC的簡單易用性就被抵銷掉了。 HDLC的軟件編程方法功能靈活,通過修改程序就可以適用于不同的HDLC應用。但程序運行占用處理器資源多,執行速度慢,對信號的時延和同步性不易預測。純軟件HDLC一般只能用于個別路數的低速信號處理。

FPGA采用硬件技術處理信號,又可以通過軟件反復編程使用,能夠兼顧速度和靈活性,并能并行處理多路信號,實時性能能夠預測和仿真。

DSP采用軟件技術處理信號,也可以反復編程使用。DSP、FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優點。在中小批量通信產品的設計生產中,用FPGA和DSP實現HDLC功能是一種值得采用的方法。

HDLC的幀結構和CRC校驗

為了使FPGA的設計能夠實現HDLC的基本功能并能按照各項標準的規定靈活采用不同的CRC校驗算法,首先看一下HDLC基本的幀結構形式。

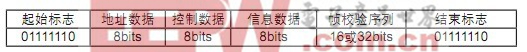

HDLC是面向比特的鏈路控制規程,其鏈路監控功能通過一定的比特組合所表示的命令和響應來實現,這些監控比特和信息比特一起以幀的形式傳送。以下是ISO/IEC 3309標準規定的HDLC的基本幀結構。

其他的HDLC標準也有類似的幀結構。每幀的起始和結束以7E(01111110)做標志,兩個7E之間為數據段(含地址數據、控制數據、信息數據)和幀校驗序列。幀校驗采用CRC算法,對除了插入的零以外的所有數據進行校驗。為了避免將數據中的7E誤為標志,在發送端和接收端要相應地對數據流和幀校驗序列進行插零及刪零操作。

用FPGA+DSP實現HDLC功能

對FPGA器件進行功能設計一般采用的是Top to Down(從頂到底)的方法,亦即根據要求的功能先設計出頂層的原理框圖,該圖通常由若干個功能模塊組成。再把各個模塊細化為子模塊,對較復雜的設計還可把各子模塊分成一層層的下級子模塊,各層的功能可以用硬件描述語言或電路圖來實現。

DSP的設計則是按軟件順序執行的方法,主函數調用子函數,還可以把子函數分成下級子函數,目前的DSP設計軟件主要是用C語言來完成。

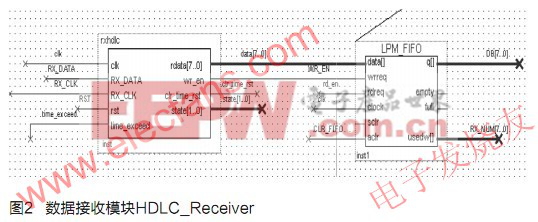

HDLC協議操作由FPGA、DSP共同完成:HDLC接收端:首先由FPGA來收數據,之后判斷幀頭“7E”及本機地址,如果是發給本機的數據,則對后續數據進行判斷,如果有5個連“1”且后一位數據為“0”則將其后的一個“0”刪除,刪零后將數據存入FIFO中,收到幀尾“7E”時給出收結束標志;然后由DSP讀收結束標志,如果標志為“1”讀空FIFO,清標志位,將數據內容進行CRC校驗。

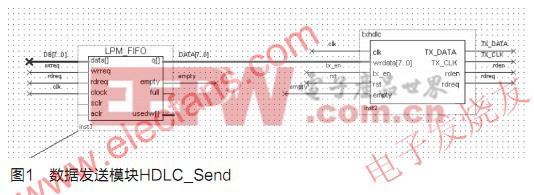

HDLC發送端:首先由DSP將數據寫入FPGA的FIFO之后,DSP給出標志;FPGA收到標志后,先發送幀頭“7E” ,然后發送數據,如果數據中有5個連“1”則在其后插入1個“0”,數據發送結束后發送幀尾“7E”。

FPGA設計

FPGA中實現的主要是鏈路層協議完成HDLC數據接口的收發,并完成與DSP的數據交互,該電路由接口模塊interface、HDLC數據發送模塊transmitter和HDLC數據接收模塊receiver三部分組成。

FPGA接口模塊interface

評論