基于VHDL和發接復用器的SDH系統設計及FPGA仿真

針對目前國內SDH系統中還沒有一個專門的E1分接復用芯征,本文介紹一種用高級硬件描述語言VHDL及狀態轉移圖完成該發接復用器的設計的新型設計方法及其FPGA實現。并給出了用Xilinx FoundaTIon tools EDA軟件設計的電路仿真波形及Spartan XCS30XL完成FPGA實現的結果。

本文引用地址:http://www.j9360.com/article/151584.htm1 數字分接復用器結構原理

本數字分接復用器的功能是:在發送端把12Mbps經過編碼的有幀結構的Ethernet(以太網)碼流分接為7路標準E1接口速率數據流,SDH 設備再把這7路數據映射到155Mbps的速率去通過光纖傳輸到下一個SDH設備;在接收端由SDH設備從155Mbps的數據流中取出7路標準E1速率數據正確恢復為原來的12Mbps的Ethernet(以太網)碼流。

發送端12Mbps有幀結構數據幀間由全1空閑碼填充。從數字分接復用器發送輸出的7路E1數據由于傳輸處理過程中路中不同,必然會造成7路E1數據在傳輸過中的各路時延不一致,這就使得各路數據不同步。在設計中如何在接收端使得7路E1數據同步,從而正確恢復原發送端12Mbps數據就成了一個難題。針對這一問題制定出了如下的解決方案。

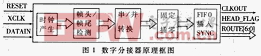

1.1 數字分接器原理框圖及說明

如圖1所示,把數字分接器從總體上劃分為:時鐘產生、幀頭/幀尾檢測、串并變換、固定插零、FIFO插入SYNC五個模塊。

在發送端,分接器的時鐘產生電路把14Mbps系統時鐘XCLK轉變為12Mbps時鐘,用這一時鐘對端口來的12Mbps成幀數據DATAIM做幀頭(1100010001)/幀尾(1000000001)檢測,檢測出幀頭后再做串/并變換操作,這樣就初步完成了分接器的功能。但是,為了使數字復接器能正確復接就需要在分接器輸出的7路數據中分別插入同步頭SYNC(0111111110)。為了使數據和插入的SYNC區別開來,須要在7路數據中每隔 7bit就固定地插入“0”。這樣,就保證了插入的SYNC不會與正常的掌握相混淆,從而也使得分接出的7路數據變為標準的E1數據。

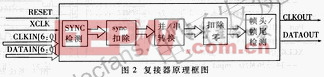

1.2 數字復接器原理框圖及說明

數字復接器原理框圖如圖2所示。與分接器相呼應,可把復接器從總體上劃分為:SYNC檢測、SYNC扣除、并/串轉換、扣除零、幀頭/幀尾檢測5個模塊。

在接收端,復接口的SYNC檢測模塊在7路E1數據流中分別檢測出7個SYNC。通過SYNC扣除模塊扣除在分接器中插入的SYNC,并使得7路 E1數據同步。之后,就可以對這7路E1數據進行并/串轉換了。對于轉換后的14Mbps數據還需要扣除在分接器中固定插入的零。根據要求對于 12Mbps的數據再一次做幀頭/幀尾檢測以便在兩幀數據之間插入全“1”的空閑碼。這樣的就正確恢復出發送端的12Mbps碼流。

在發送端和接收端所有SYNC的處理都用FIFO技術來實現。電路設計采用硬件高級描述語言VHDL和狀態機來完成,用FPGA驗證實現。為提高電路的可實現性,設計全部采用D觸發器和邏輯門來實現,并且綜合約束工具來控制FPGA內部電路的路徑延時。

2 VHDL語言設計相對于傳統設計的優點

(1)采用自頂向上(Top Down)的設計方法

與傳統的系統硬件設計從具體的設計單元開始不同,VHDL設計是從系統的總體要求出發,先進行系統建模仿真,仿真通過后再利用VHDL層次化、結構化及行為化的描述方法將各個模塊模型用可實現的VHDL電路描述替換。這對于一個非常大的硬件系統設計從總體上把握設計的可行性是非常重要的。

(2)采用系統的早期仿真

通過對系統建模的早期仿真便于在系統設計的早期發現設計中潛在的問題,與傳統的自下而上設計的后期仿真相比可大大縮短系統設計的周期。

(3)降低了硬件電路的設計難度

不需要象傳統的設計方法在設計前就要寫出電路的邏輯表達式、真值表及卡諾圖化簡,VHDL在設計計數器的時候只關心計數器的狀態就可以了。這樣也大大縮短系統設計的周期。這對于時間效益的現代社會是非常重要的。

(4)VHDL設計文檔的靈活性

用VHDL設計硬件電路,主要的設計文件是用VHDL編寫的源程序。如果需要也可以利用EDA軟件轉化為原理圖。另外,它資源量小,便于保存,可以方便地被其它設計所利用,可繼承性好,在源文件中可方便地加入注釋,可讀性好。

3 分接復用器的VHDL及狀態轉移圖設計

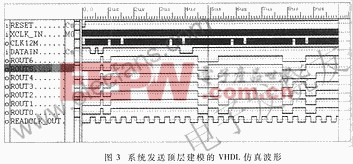

3.1 分接復用器頂層VHDL建模(Top level)及系統功能仿真

(1)系統發送頂層建模的VHDL端口描述

Library IEEE;

Use IEEE.std_logic_1164.all;--引用庫說明;

EnTIty TRAN_TOP is

Port (RESET : IN STD_LOGIC;--ststem reset signal;

XCLK_IN : IN STD_LOGIC;--14.336MHz input high clock;

DATAIN : IN STD_LOGIC;--12.544MHz input data;

CLK12M :OUT STD_LOGIC;--12.544MHz input clock;

READCLK_OUT:OUT STD_LOGIC;--2.048 MHz output clock;

ROUT:OUT STD_LOGIC_VECTOR(6 downto 0)-2.048 MHz 7 route -output data;

);

end TRAN_TOP;

(2)系統發送頂層建模的VHDL仿真波形

評論