基于ARM開發的JTAG仿真器的調試設計

基于JTAG仿真器的調試是目前ARM開發中采用最多的一種方式。大多數ARM設計采用了片上JTAG接口,并將其作為測試、調試方法的重要組成。

本文引用地址:http://www.j9360.com/article/151238.htmJTAG仿真器通過ARM芯片的JTAG邊界掃描口與ARM CPU核通信,實現了完全非插入式調試,不使用片上資源,不需要目標存儲器,不占用目標系統的任何端口。由于JTAG調試的目標程序是在目標板上執行,使得仿真更加接近于目標硬件[1]。

目前針對嵌入式系統開發的調試工具品種繁多,如ARM公司的AXD debugger軟件與Mutil-ICE仿真器等。但是大部分嵌入式調試工具價格過高,因此設計實現一種速度快、性能穩定、價格低廉、易于實現的ARM調試工具是十分必要的。

1 ARM JTAG調試原理

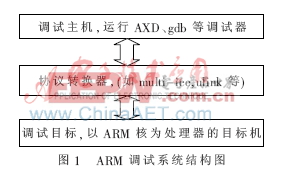

ARM典型的調試系統結構如圖1所示。調試系統包括調試主機、仿真器和調試目標。

調試主機是一臺運行調試軟件(例如ADS)的計算機。調試主機可以發出高層的調試命令,例如設置斷點、訪問內存等[2]。

仿真器用來將調試主機發出的高層調試命令轉換為底層的ARM JTAG調試命令。因為目標機無法識別調試主機發送來的高級命令,因此就需要仿真器將調試主機發出的高層調試命令轉換為底層的ARM JTAG調試命令[3]。在整個調試系統中起到重要的作用,其性能也決定了整個調試系統性能。

2 方案設計

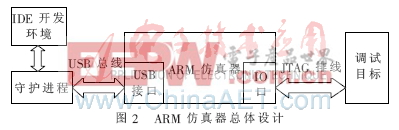

本文提出了一種采用PHILIPS公司的ARM7芯片LPC2148設計,具有USB2.0通信方式、高速穩定的ARM仿真器實現方案,如圖2所示。

守護進程接收從IDE集成開發環境發送來的調試命令,將其通過USB總線轉發到ARM仿真器,ARM仿真器再將調試命令轉換成JTAG格式的信號并發送到I/O口,從而控制調試目標執行特定的操作,達到調試的目的。同理,從調試目標返回的數據,先經過ARM仿真器的譯碼,再經過守護進程返回到IDE開發環境,從而形成一個完整的調試系統。

3 硬件電路設計

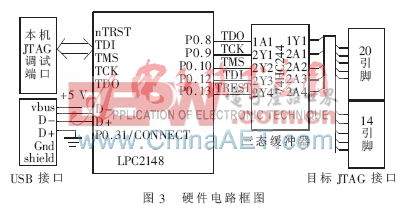

本設計的最大特點是采用了LPC2148作為主控芯片。該芯片內部集成了ARM7TDMI-S微控制器和完全兼容USB2.0的設備控制器,支持32個物理(16個邏輯)端點;支持控制、批量、中斷和同步端點;所有端點都有一個雙向的DMA通道。因為芯片內部集成了USB控制器,大大降低了電路板的設計難度和開發成本。其硬件電路框圖如圖3所示。

(1)本機JTAG調試電路

為了便于調試和燒寫程序,將芯片LPC2148的JTAG接口接到一個20引腳的標準JTAG插口。本設計中使用引腳P0.8、P0.9、P0.10、P0.12、P0.14作為外部JTAG接口,盡量不用有其他接口功能的引腳,如P0.11、P0.14接口與I2C接口SCL1、SDA1功能復用,以便于將來的硬件升級。為了增強帶負載能力,使用一片74HC244芯片,同時為了盡量兼容大部分ARM開發板上的不同JTAG插口,本設計提供了一個20引腳的JTAG插口和一個14引腳的JTAG插口。

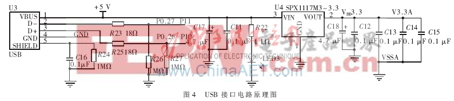

(2)USB電路(包括供電電路)

USB接口電路如圖4所示。為了使LPC2148的軟件可以更靈活地控制USB設備與主機之間的連接,本接口電路使用P0.31(只能使用該引腳)來實現SoftConnect特性。當P0.31輸出低電平時,D+線通過電阻上拉到VDD3.3,通知USB主機:USB設備與其建立連接;當P0.31輸出高電平時,D+線斷開與VDD3.3的連接,通知USB主機:USB設備已經斷開與USB主機的連接。

Q1選用的是P溝道MOS管,而不選用普通的PNP三極管,因為MOS管是電壓驅動型,驅動電流幾乎為0;而普通的PNP三極管是電流驅動,需要一定的驅動電流。導通時,P0.31_P17有可能被拉低,LPC2148要求該引腳在復位引腳為低電平期間不能被拉低,否則JTAG口將被禁止,因此必須選用P溝道的MOS管。LPC2148的P0.23引腳為USB設備控制器,用于檢測USB總線是否插入檢測引腳[4]。

4 仿真器固件程序設計

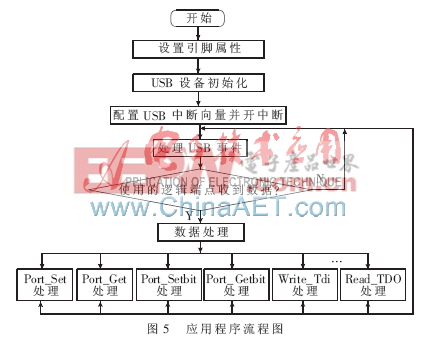

仿真器LPC2148芯片中的固件程序實現的功能包括:通過USB與上位機軟件進行通信,并將上位機發送過來的、經過封裝的USB數據流轉換為JTAG信號,并最終送到相應的引腳或者將相應引腳的數據經過封裝后,通過USB傳送到PC機中。圖5為應用程序的流程圖。

評論