TMS320C31和80C196雙CPU構成的高速實時控制

介紹了采用TMS320C31和80C196雙CPU構成的高速實時控制系統的基本構成,給出了TMS320C31、80C196與雙口RAM IDT7140之間的接口電路,IDT公司雙口RAM系列的中斷邏輯設計以及DPS與80C196之間采用雙口RAM進行高速數據通信的軟件實現。該控制系統可應用于對實時性要求很高的系統中。

本文引用地址:http://www.j9360.com/article/151089.htmDSP也稱數字信號處理器。TMS320C31是TI公司的第三DSP芯片,它的基本結構包括:(1)程序文憑間與數據空間分開的總線結構,可以對程序存儲器和數據存儲器這兩個獨立的存儲器進行獨立編址、獨立訪問;(2)流水線結構,以三級流水線操作為例,在每個指令周期內,三條不同的指令都處于激活狀態,但處于不同的階段,分別為取指、譯碼和執行;(3)專用的硬件乘法器,使乘法可以在單周期內完成;(4)特殊的DSP指令;(5)快速的指令周期,可以達到33.3ns,即每秒能執行60M條指令。

由一片TMS320C31加上存儲器、模/數轉換單元和外設接口就可以構成一個完整的控制系統,但這種方案若要達到高速實時控制則是不可行的。因為TMS320C31除要完成復雜的算法,還要采集處理數據、控制外部系統中的執行機構和實現人機接口等功能,而這些工作勢必會大大延長系統對控制對象進行控制的周期。所以我們采用TMS320C31和一個通用微處理器80C196一起來作為這個高速實時控制系統的CPU。其中80C196作為主機,負責數據的采集處理、外部系統中執行機構的控制和驅動以及人機接口等功能;TMS320C31作為從機,負責復雜算法的實現。這樣可以使TMS320C31專注于算法的計算,充分利用它高速數據處理的能力。TMS320C31與80C196之間通過雙口RAM進行高速數據通信,之所以采用雙口RAM是因為這種通信方式數據傳輸的速率很高,并且抗干擾性能較好。

1 系統構成

系統主要由兩大模塊組成:算法模塊和輸入輸出控制模塊。算法模塊以TMS320C31為核心構成,是整個系統的計算中心,負責復雜算法的實現;輸入輸出控制模塊以80196為中心構成,負責數據的采集處理、外部系統中執行機構的控制和驅動以及人機接口等功能。算法模塊與輸入輸出控制模塊之間通過雙口RAM IDT7140進行高速數據通信。算法通過從輸入輸出控制模塊處獲得算法所需的輸入數據(即實時采樣到的數據),然后將計算結果送給輸入輸出控制模塊,最后再由輸入輸出控制模塊控制各執行機構。

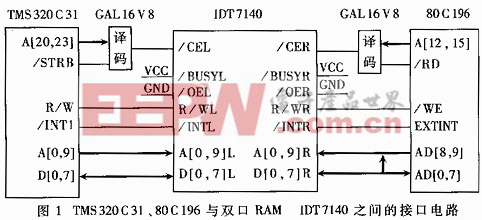

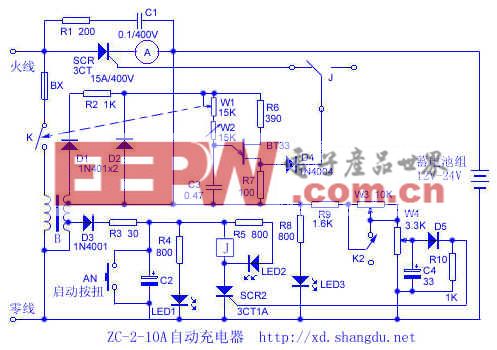

2 TMS320C31、80C196與雙口RAM IDT7140之間的接口電路

如圖1所示,IDT7140有兩組完全對稱的地址線數據線和控制線, TMS320C31與左邊這組線相連,80C196與右邊的那組線相連。TMS320C31給IDT7140分配的地址空間為0x20000H~0x1003ffH。通過GAL16V8對A[20,23]和外部存取選通信號/STRB進行譯碼,給出IDT7140的片選信號/CEL。IDT7140通過/BUSYL和/BUSYR引腳接高電平,工作在中斷方式。IDT7140的中斷信號/INTL可以與TMS320C31的某個外部中斷引腳直接相連(這里將外部中斷1即INT1分配給雙口RAM IDT7140),具體原因將在第3部分進行說明。80C196給IDT7140分配地地址空間為0xA000H~0xA3ffH。通過GAL16V8對AD[12,15]和外部存儲器讀信號/RD進行譯碼,給出IDT7140的片選信號/CER。80C196的/WE在寫周期為低電平,讀周期為高電平,與IDT7140的R/WR定義一致,所以/WE可直接與R/WE可直接與R/WR相連,作為IDT7140右邊的讀之所以控制信號。IDT7140的中斷引腳/INTR接到80C196的外部中斷。

TMS320C31與左邊這組線相連,80C196與右邊的那組線相連。TMS320C31給IDT7140分配的地址空間為0x20000H~0x1003ffH。通過GAL16V8對A[20,23]和外部存取選通信號/STRB進行譯碼,給出IDT7140的片選信號/CEL。IDT7140通過/BUSYL和/BUSYR引腳接高電平,工作在中斷方式。IDT7140的中斷信號/INTL可以與TMS320C31的某個外部中斷引腳直接相連(這里將外部中斷1即INT1分配給雙口RAM IDT7140),具體原因將在第3部分進行說明。80C196給IDT7140分配地地址空間為0xA000H~0xA3ffH。通過GAL16V8對AD[12,15]和外部存儲器讀信號/RD進行譯碼,給出IDT7140的片選信號/CER。80C196的/WE在寫周期為低電平,讀周期為高電平,與IDT7140的R/WR定義一致,所以/WE可直接與R/WE可直接與R/WR相連,作為IDT7140右邊的讀之所以控制信號。IDT7140的中斷引腳/INTR接到80C196的外部中斷。

評論