它的基本結構包括:(1)程序文憑間與數據空間分開的總線結構 文章 進入它的基本結構包括:(1)程序文憑間與數據空間分開的總線結構技術社區

TMS320C31和80C196雙CPU構成的高速實時控制

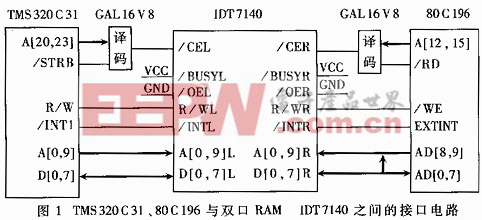

- TMS320C31和80C196雙CPU構成的高速實時控制,介紹了采用TMS320C31和80C196雙CPU構成的高速實時控制系統的基本構成,給出了TMS320C31、80C196與雙口RAM IDT7140之間的接口電路,IDT公司雙口RAM系列的中斷邏輯設計以及DPS與80C196之間采用雙口RAM進行高速數據通信的

- 關鍵字:

DSP 雙口RAM 高速實時 中斷

DSP也稱數字信號處理器。TMS320C31是TI公司的第三DSP芯片

它的基本結構包括:(1)程序文憑間與數據空間分開的總線結構 可以對程序存儲器和數據存儲器這兩個獨立的存儲器進行獨立編址、獨立訪問 (2)流水線結構 以三級流水線操作為例 在每個指令周期內 三條不同的指令都處于激活狀態 但處于不同的階段 分別為取指、譯碼和執行 (3)專用的硬件乘法器 使乘法可以在單周期內完成 (4)特殊的DSP指令 (5)快速的指令周期 可以達到33.3ns 即每秒能執行

| 共1條 1/1 1 |