基于現代DSP技術的QPSK調制器的設計

摘要:為了提高DSP系統的開發效率,引入了現代DSP技術,并由此設計了QPSK調制器。依據QPSK調制的基本原理,利用MATLAB/Simulink DSP Builder和Quartusll搭建模型,在模塊的形成方式上,采用DSP Builder中的模塊代替VHDL編程,在同一平臺上實現了系統建模和硬件實現的有機結合,然后利用ALTERA公司提供的Signal Compile進行編譯,產生VHDL源程序,同時,采用ALTERA公司的Cyclone系列芯片EP2C35F6 72C6N實現QPSK調制。結果表明,該方法提高了設計的靈活性,通過軟件仿真和硬件測試驗證了方案的正確性和可行性。

關鍵詞:四相相移鍵控調制;FPGA;現代DSP技術;QuartusⅡ

四相相移鍵控調制(Quaternary Phase Shift Keying,QPSK)是一種線性窄帶數字調制技術,它已經在數字調制技術中占有重要的地位,被廣泛地應用于衛星通信、移動通信、視頻會議系統、蜂窩電話和其它數字通信領域。具有頻帶利用率高、頻譜特性好、抗衰落性能強、較低的比特錯誤率等優點。

DSP技術主要是指將DSP的基本理論和算法付諸實現的途徑和方法。傳統的DSP技術是當前廣泛使用的DSP處理器的解決方案,而這種解決方案日益面臨著不斷增加的巨大挑戰,自身的技術瓶頸導致這種解決方案在DSP許多新的應用領域中的道路越走越窄。而現代DSP技術是相對于傳統DSP技術而言的,是基于可編程片上系統SOPC(System on a Programmable Chip)技術、EDA技術與FPGA實現方式的DSP技術,是現代電子技術發展的產物,它有效地克服了傳統DSP技術中的許多瓶頸,在許多方面顯示了突出的優勢,如高速與實時性,高可靠性,自主知識產權化,系統的重配置與硬件可重構性,單片DSP系統的可實現性以及開發技術的標準化和高效率。QPSK設計采用MATLAB/Simulink DSP Builder開發出用于QPSK調制的正交信號產生單元,在電路模塊的形成方式上用DSP Builder的模塊調用代替繁瑣的VHDL程序,從而方便的得到了所需的結果。系統的實現以FPGA為物理載體,與傳統的基于硬件描述語言的設計相比,這種流程更快捷方便靈活。

1 QPSK調制原理

所謂的QPSK調制就是利用載波的四種不同相位來表征數字信息,每一種載波相位代表兩個二進制代碼元信息。由于每一個載波相位代表兩個二進制碼元信息,所以每四個二進制碼元又被稱為雙比特碼元。

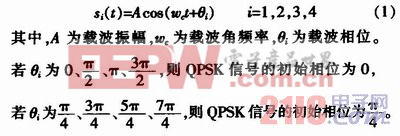

QPSK信號的表示式為

將式(1)寫成

I(t),Q(t)為+1或-1。則式(3)即為QPSK的數學表達式。

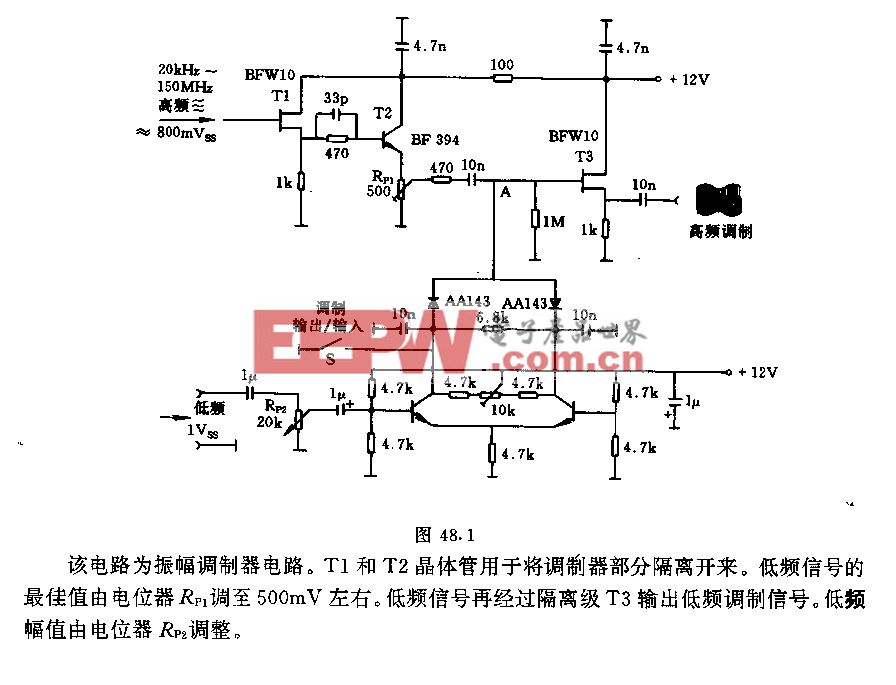

QPSK信號的調制可分為相位選擇法和調相法,本文采用調相法進行設計,其調制框圖如下圖1所示。

圖1中,串/并變換器將輸入的二進制序列依次分為兩個并行的雙極性碼序列。設二進制數分別為a和b。雙極性的a和b脈沖通過兩個平衡調制器分別對同相載波和正交載波進行二相調制,兩路輸出疊加后就可以得到QPSK信號。

2 基于DSP Buildter的QPSK設計

DSP Builder可完成圖形化的系統建模、設計、仿真、把設計軟件下載到FPGA開發板上。它是一個系統級的開發工具,架構在多個軟件之上,并把系統級和RTL級兩個設計領域的設計工具連接起來,最大程度的發揮了兩種工具的優勢。DSP Builder依賴MathWorks公司的數學分析工具Matlab/Simulink,以Simulink的Blockset出現,可以在Simulink中進行圖形化設計和仿真,同時通過SignalCompiler可以把Matlab /Simulink的設計文件(.mdl)轉成相應的硬件描述語言VHDL設計文件(.vhd),以及用于控制綜合與編譯的TCL腳本。而對后者的處理可以由FPGA/CPLD開發工具QuartusⅡ來完成。

評論