基于FPGA+DSP的高速中頻采樣信號處理平臺的實現

摘要:高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。實驗與實際應用表明,該系統具有很強的數據處理能力和很好的穩定性。

關鍵詞:高速中頻;信號處理;FPGA;DSP

0 引言

現代社會正向數字化、信息化方向高速發展,在這一過程中,往往需要高速信號的實時性數字化處理。例如,隨著科技的進步,現代雷達等應用信號的數字化處理上有了長足的發展,但也帶來了新的問題,這些應用的數字信號處理具有海量運行需求的應用背景,如巡航導彈末制導雷達地形匹配、合成孔徑雷達的成像處理、相控陣雷達的時空二維濾波處理等領域。目前,單片DSP難以勝任許多信號處理系統的要求。而常見的解決方案也是高速A/D采樣與信號處理功能是在多塊不同的板卡上實現,這給實際應用帶來很多不便。

鑒于上述現有技術所存在的問題,本設計平臺的目的是:

(1)實現高速中頻信號(如雷達信號)的數字化處理并進行實時傳輸數據或進行數據的實時計算,并能通過輸出電路進行結果顯示;

(2)自定義控制總線可以實現對高速中頻信號處理板進行靈活控制,具有較強的可配置性和豐富的靈活性;

(3)高速A/D采樣與D/A回放及數據處理單元集成在一塊板上,在集成度高的同時也降低了高速信號在傳輸過程中出現差錯的概率。

1 平臺設計方案

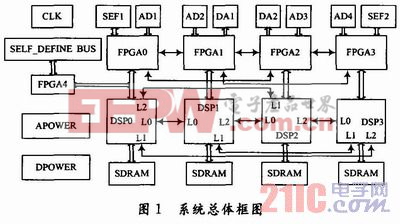

高速中頻采樣信號處理平臺由主控制電路、高速A/D與D/A電路、信號處理單元電路、光纖通道電路、時鐘管理電路、存儲單元和外部接口電路組成,其總體框圖如圖1所示。

在實際應用過程中,四路A/D通道可以接收不同的信號源的信號,D/A通路可以對外進行數據顯示等多種功能,時鐘管理電路管理內外時鐘的使用及對板上系統供給工作時鐘,兩路光纖通道可以與其他高速設備相連接,自定義總線可以與CPU或主控制器相連接對平臺進行有效靈活的控制。

評論