DA算法的FIR濾波器設計

1.引言

在數字信號處理系統中,FIR數字濾波器多采用專用DSP芯片(如TMS320CXX系列),這種基于DSP的處理系統存在很多優點,比如方案靈活、可操作性強、程序易于移植。但這種結構的濾波器多是根據FIR 濾波器的數據移位相乘累加的算法編寫相應軟件,利用軟、硬件相互結合完成濾波器的設計。由于軟件運行時,指令都是串行執行的,這嚴重制約了系統的運行速率,不能滿足高傳輸速率,大數據吞吐量的數字信號的實時性處理要求。而基于DA算法的FPGA濾波器則是一種采用純硬件的方式實現FIR 濾波器的方式,這種方法突出的優點是運算速度快,特別適合在高速、實時、快變的數字信號處理要求。

2.DA算法的基本思想

第一個討論分布式算法(distributed arithmetic,DA)的可以追溯到1973年Cr0i Croisier的一篇論文,并由Peled和Liu來推廣。但是直到FPGA出現以后,才在FPG計算乘積和中被廣泛地應用。在FPGA 芯片設計中,分布式算法(distributed arithmetic,DA)是一種很重要的技術。它在乘積和的計算中已被廣泛應用,為了理解DA算法設計原理,我們考慮有一個線性時不變網絡的輸出可以用下式表示:

假設系數c[n]是已知常數,x[n]是變量,在有符號DA系統中假設變量x[n]的表達式如下:![]()

其中xb[n]表示 x[n]的第b位,即x[n]是x第n個樣點。所以,內積y 可以表示為:![]()

我們重新分別求和次序(這就是分布式算法的由來),結果是:

y=(c[0]xB-1[0]+c[1]+……+c[N-1]xB-1[N-1])2B-1+(c[0]xB-2[0]+c[1]+……+c[N-1]xB-2[N-1])2B-2 (2-4)

.

.

.

+(c[0]x0[0]+c[1]x0[1]+c[N-1]x0[N-1])20

用更緊湊的形式表示為:![]()

從(2—4)式可以發現,分布式算法是一種以實現乘加運算為目的的運算方法。它與傳統算法實現乘加運算的不同在于執行部分積運算的先后順序不同。分布式算法在實現乘加功能時,是通過將各輸入數據的每一對應位產生的部分積預先進行相加形成相應的部分積,然后再對各個部分積累加而得到最終的結果,而傳統算法是等到所有乘積已經產生之后再來相加完成乘加運算的。與傳統串行算法相比,分布式算法可極大地減少硬件電路的規模,提高電路的執行速度。

3.基于DA算法的FIR數字濾波器的硬件實現

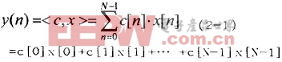

由上面分析可以知道,對于任何一個線性時不變網絡總可以將它轉換成式(2-5)那樣的形式,FIR濾波器是一個很典型的線性時不變網絡,它的表達式是:![]()

我們可以將它轉化成下面這樣的形式:![]()

在本系統中,采用的是8 位輸入,所以B = 8 則:![]()

線性相位FIR濾波器滿足系數對稱條件,本系統設計的系統為16階,那么它的系數關于h[7]偶對稱,即有:

h[n]= h[16-1-n]= h[15-n] (3-4)

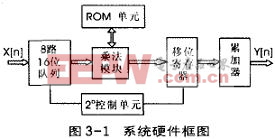

由式(3-3)和(3-4)可得到實現系統硬件框圖如圖3-1:

4.系統的VHDL描述

4.1頂層模塊設計

Library ieee;

Use ieee.std_logic_1164.a11;

Use ieee.std_logic_unsigned.all;

Entity FIR is

Port (x: in std_logic_vector(7 downto 0);

clk : in std_logic;

y : out std_logic_vector(7 downto 0));

end FIR;

architecture behave of FIR is

component lpfir

port (

in : in std_logic_vector(7 downto 0);

clk : in std_logic;

out : out std_logic_vector(7 downto 0));

end component ;

begin

process(clk)

begin

u1:lpfir port map (x,clk,y);

end process;

end behave;

4.2 LUT查詢表ROM的建立

用MIF文件格式編輯的ROM初始化值

WIDTH = 16

DEPTH = 16

ADDRESS_RADIX = HEX ;

評論