高性能32位移位寄存器單元的設計

1 引言

本文引用地址:http://www.j9360.com/article/150524.htm 本文給出了一種可用于32位以上CPU執行單元的移位寄存器電路,并針對CISC指令集INTEL X86進行了優化(由于RISC指令集中移位類指令實現比較簡單,故沒有在文中討論);采用指令預處理的技術和通過冗余位,能很方便的實現帶進位標志 CF移位和設置CF位,并使得每條移位指令的平均執行速度為兩個指令周期。它有效地提高了CPU對移位類指令的執行性能,并且作為一個基本的內核單元能很方便地移植到不同指令集(RISC或 CISC)的CPU設計之中。

2 32位CPU中執行單元總體結構

我們所設計的32位CPU的執行部分采用雙總線結構,數據總線(Abus,Bbus)的寬度是32位。由于移位類指令如果用ALU進行實現的話,必然會耗費太多的CPU周期,為實現在一個指令周期內對32位數據進行任意位的移位操作,因此有必要在執行單元中設計專用硬件移位寄存器,在執行移位類指令時由它進行32位數據的移位。

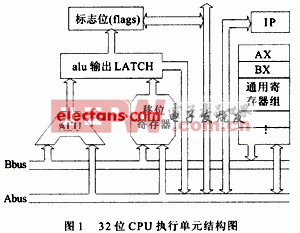

圖1給出了32位CPU執行單元總體結構數據流結構簡圖,并省略了所有控制信號。圖中Abus為雙向32數據總線,Bbus為單向32位數據總線。由于考慮到要實現INTEL X86系列所有的移位類指令(RCR,RCL,ROR,ROL等),所以移位寄存器在設計時采用雙輸入端,即實際該移位寄存器最大能實現64位移位。通過特殊的指令預設置方法,并通過增加冗余位實現標志位的設置。

3 移位寄存器單元的設計

3.1 矩陣移位器和樹狀移位器

在CPU中移位寄存器單元的設計一般采用的是矩陣結構和樹狀結構的移位器。

3.1.1 矩陣結構(Matrix Style)移位器

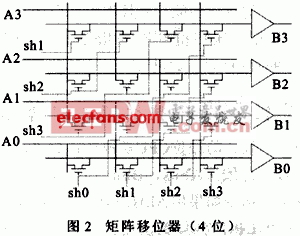

它的結構為一傳輸門組成的陣列。行數等于操作數據寬度,列數等于最多能移位數如圖2所示(以4位舉例)。

其中A3~A0是4位數據輸入線,sh3~sh0是 4根控制信號線。每次進行N位移位操作,對應的shN為高,其它控制信號為低。

這種結構的優點是:(1)數據傳輸的速度快,每個信號到達輸出端只經過了一級傳輸,不受移位器位數限制;(2)版圖很規整。缺點是:(1)每根控制信號的負載太大,如32位移位器,每根信號線(sh0,sh1,……sh31)都要驅動32個開關管;(2)所需晶體管數目太多,如n位移位器所需晶體管數為2× n×n=2n2 (傳輸門部分采用CMOS實現),所帶來的功耗和芯片面積也會增加;(3)每一移位操作只需一根控制線為1,所以需輔以額外的譯碼單元。

評論