DSP芯片的Flash存儲器的在線編程方式

在嵌入式系統中,為了實現程序的脫機自動運行,程序往往固化在電可擦除的Flash存儲器中。要實現一個嵌入式系統的帶電脫機運行,在線編程就成為嵌入式系統開發過程的必經之路。由于在線編程涉及到硬件和軟件方面的內容,因此要從頂層設計和系統的角度來考慮在線編程。硬件設計要為軟件設計作鋪墊,盡可能簡化軟件設計。

本文引用地址:http://www.j9360.com/article/148916.htm本文以TI公司的DSP芯片TMS320C6711D和AMD公司的4 Mb Flash存儲器AM29LV400B為例來介紹兩種在線編程方式。

1.1 以Ready信號作為硬件握手

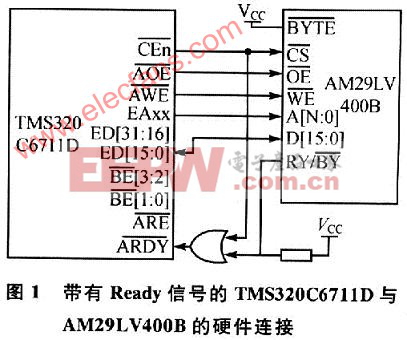

帶有Ready信號的TMS320C6711D的EMIF(Exterhal Memory InteRFace)接口與Flash存儲器AM29LV400B的硬件連接如圖1所示。由于AM29LV-400B輸出的就緒信號/忙信號()為OD(漏極開路)輸出,需要在該信號上加上拉電阻并連接到VCC。

1.2 采用無Ready硬件連接的軟件握手

不帶Ready信號的TMS320C6711D與Flash存儲器AM29LV400B的硬件連接如圖2所示。

2 軟件設計

2.1 帶有硬件握手的軟件設計

帶有Ready信號連接的Flash存儲器編程時序如圖3所示。Flash的就緒信號/忙信號()輸出為低電平時,表明Flash正忙,處于編程或擦除狀態。由于DSP與Flash存儲器采用Ready/Busy信號作為硬件握手信號,當Ready/Busy信號為低電平時,CPU在總線時序上插入等待周期,直到Ready/Busy信號解除(為高電平)。在Ready信號為低電平期間,由于CPU處于等待狀態,程序被暫停執行,因此不需要通過軟件來判斷Flash存儲器的編程或擦除狀態。

存儲器相關文章:存儲器原理

評論