基于DSP+FPGA的磁鐵電源控制器的設計

摘要:介紹了一種基于DSP和FPGA的磁鐵電源控制器的設計方案,闡述了該控制器硬件系統的組成,包括信號調理電路、中間數據處理部分、后端的驅動電路。同時給出了DSP和FPGA之間通過SPI接口通信的具體流程和輸出PWM波形死區部分的控制流程。設計的磁鐵電源控制器有很好的控制和運算能力,同時具有很好的靈活性和可靠性。

關鍵詞:磁鐵電源控制器;DSP;FPGA;SPI

磁鐵電源大多作為電源中的一種特種電源被廣泛應用于加速器、質譜儀等設備,為磁鐵提供特定的勵磁電流以產生所需的磁場,對磁鐵電源的基本要求來源于磁場特性,因此基于數字化電源控制器的磁鐵電源為輸出高精度的穩定勵磁電流,以獲得符合運行模式的穩定磁場結構提供了重要保證。文中介紹的磁鐵電源控制器采用DSP和FPGA的雙CPU結構,采用FPGA控制高精度模數轉換器AD7679進行采樣,通過DSP的SPI接口把采集到的數據送給DSP;由DSP運算處理后輸出用來控制磁鐵電源的帶有死區的PWM波形。

1 控制器總體結構

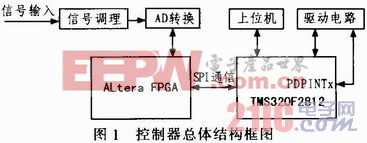

控制器采用DSP TMS320F2812為數字處理輸出模塊,以Altera公司的CvcloneⅢ系列FPGA控制前端AD進行數據采集,數據傳輸部分由FPGA與DSP的SPI接口完成。通過DSP的SCI串口與上位機實現通訊,顯示并控制電源的運行狀態,后端的驅動電路中實現主電路和驅動電路的隔離。控制器總體結構框圖如圖1所示。

2 硬件電路設計

2.1 信號調理電路

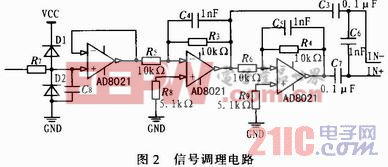

信號調理電路的主要作用是實現信號的放大和低通濾波。因為要保證將AD轉換器的采集信號限制在0~+5 V之間,為防止大電流信號時產生過高的輸入電壓會損壞A/D端口,設計了電平限制保護電路。AD轉換器輸入采用差分輸入方式,將單端信號轉換為差分信號,實現比例放大,有效的濾除了高頻噪聲,便于AD對輸入信號的高精度采集。圖2為信號限幅、隔離、濾波和放大電路。

2.2 FPGA對AD的控制

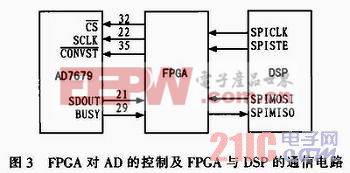

本設計采用的AD7679是18位電荷分配的完全差分逐次逼近型模數轉換器,具有570 ksps的采樣速率,同時可以與5 V或3 V的數字邏輯電平兼容。為防止采樣點在開關脈沖之上,系統出現振蕩,可以使DSP在發出開關脈沖的同時給FPGA一個同步信號,作適當延時,等信號的尖峰脈沖消失后,FPGA再給ADC發出采樣命令。AD操作分為空閑、開始AD轉換、等待AD轉換、讀AD轉換結果4個狀態。在CONVST信號的下降沿后,開啟轉換過程,BUSY會自動置1,保持轉換。當BUSY信號變為低電平,CONVST保持高電平時,AD7679處于數據采集階段。FPGA對AD的控制如圖3所示,實際的電路中,FPGA和AD轉換器之間加入四通道的磁隔離器件ADuM1412進行數據隔離。

2.3 DSP與FPGA間的通信

TMS320F2812內部帶有一個SPI接口,通過定義控制寄存器。設置DSP為主設備,為通信提供時鐘信號,FPGA作為從設備。由于DSP和FPGA的I/O口引腳電壓相匹配(3.3 V),所以不需要電平轉換電路。設置FPGA在時鐘脈沖上升沿時發送數據,在下降沿時接收數據。由于FPGA發送的數據時總是將最高位的數據移出,接著將剩余的數據分別左移一位,所以DSP將接收到的數據逐位左移實現數據接收。當SPISTE引腳為低電平時,FPGA逐位發送數據;當SPICLK引腳為高電平時,DSP逐位讀取數據,并且左移一位后等待下一次SPICLK為高電平,當SPISTE為高電平時,則DSP已經接收完FPGA發送的數據,經過8個時鐘脈沖后,完成一次SPI時序,DSP將接收到的數據存儲到已經定義的數組中。DSP與FPGA通信引腳連接如圖3所示。

評論