基于ARMS和FPGA的嵌入式數控系統設計

摘要:提出了一種基于ARM和FPGA的嵌入式數控系統設計方案。詳細介紹了ARM系統的軟硬件設計,基于FPGA的硬件精插補實現方法以及數控系統的加減速控制策略。該系統將ARM運行速度快、計算精度高的優點和FPGA內部邏輯的在線可重構性等特點相結合,提高了資源利用率和實時性,增強了數控系統的靈活性。仿真和實踐結果表明,整個控制系統具有實時性好、低成本、高性能等優點。

關鍵詞:ARM;FPGA;數控系統;插補

0 引言

現有的數控系統中多采用工控機加運動控制卡的計算機數控系統方案進行運動控制器的設計。隨著工控機整體功能日趨復雜,對運動控制系統的體積、成本、功耗等方面的要求越來越苛刻。現有計算機數控系統在運動控制方面逐漸呈現出資源浪費嚴重、實時性差的劣勢。此外,數控系統的開放性、模塊化和可重構設計是目前數控技術領域研究的熱點,目的是為了適應技術發展和便于用戶開發自己的功能。本文基于ARM和FPGA的硬件平臺,采用策略和機制相分離的設計思想,設計了一種具有高開放性特征的嵌入式數控系統。該數控系統不僅具備了以往大型數控系統的主要功能,還具備了更好的操作性和切割性能,而且在開放性方面優勢更為突出,使數控系統應用軟件具有可移植性和互換性。

1 基于ARM和FPGA的嵌入式數控系統整體方案

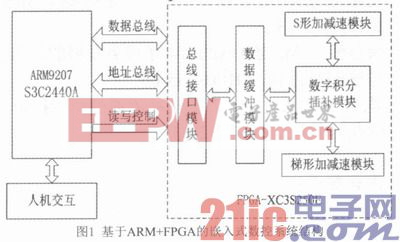

基于ARM和FPGA的嵌入式數控系統結構如圖1所示。按照模塊劃分的思想,本文將控制器分為人機交互、插補算法和通信三部分。系統中ARM采用三星公司推出的16/32位RISC微處理器S3C2440A,它采用了ARM920T內核,核心頻率高達400MHz。FPGA采用Xilinx公司Spartan 3E系列的XC3S250E。

2 S3C2440A控制系統

ARM作為數控系統的控制核心主要負責對從數據存儲器中讀取或直接從上位PC或網絡獲得的零件加工代碼和控制信息進行譯碼、運算、邏輯處理,完成加工數據的粗插補以及人機界面和數據通信。ARM系統是整個數控系統的控制核心,在嵌入式操作系統的管理下,采用分時處理的方式實現整個系統的信息處理和粗插補運算,通過鍵盤、觸摸屏等輸入裝置輸入各種控制指令,對數控系統的實時運行狀態通過LCD、指示燈等顯示,實現人機友好交互。基于S3C2440A控制器有各種通信接口,包括RS232、RS485、以太網口、USB等接口模塊。通過這些接口實現文件傳輸和網絡控制。

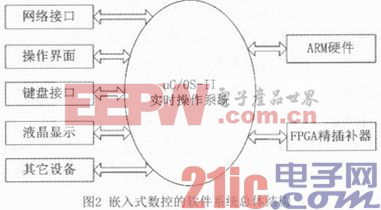

嵌入式數控的軟件系統總體結構如圖2所示。系統的軟件結構主要分為兩部分:操作系統軟件和數控應用軟件。由于數控系統是個實時多任務系統,實時性要求很高,為保證各個任務的協調執行,本系統采用了μC/OS-II實時操作系統作為軟件平臺。

要實現該操作系統在S3C2440A微處理器平臺上的正常運行,需要修改與處理器類型有關部分的代碼,操作系統移植需要完成的工作是改寫三個文件,即改寫文件0S_CPU.H、0S_CPU_A.ASM和OS_CPU_C.C。其中0S_CPU.H包括了用#define語句定義的,與處理器相關的變數、宏和類型。0S_CPU_A.ASM中定義了幾個匯編語言函數,包括中斷服務程序的中斷向量地址等。如果某些C編譯器允許在C語言中直接插入匯編語言語句,就不一定需要,用戶可以把所需的匯編語言代碼直接放到OS_CPU_C.C文件中。

3 ARM和FPGA的接口設計

為使系統能夠按照預期設計良好工作,首先要從硬件上實現ARM和FPGA之間的可靠通信。本文采用的方案是在FPGA上實現SRAM時序,將FPGA作為一塊特殊的內存設備掛接到ARM的內存地址空間。這樣在ARM端只需要編寫SRAM的驅動程序就可以實現對FPGA端的數據寫入和讀取。

3.1 SRAM時序

SRAM時序分為讀時序和寫時序兩種。當CPU對SRAM進行讀操作時,首先會在地址線上寫入正確的地址信號,接著是對SRAM芯片的片選信號,然后是對芯片的讀信號,之后經過一定的振蕩期后CPU在數據線上讀到穩定的有效數據。

當CPU對SRAM進行寫操作時,首先會在地址線上寫入正確的地址線號,接著是對SRAM芯片的片選信號,然后是對芯片的寫信號,在寫信號上升沿之前CPU會在數據線上準備好有效數據,以供SRAM芯片在寫信號上升沿將數據寫入相應的地址單元。

fpga相關文章:fpga是什么

c語言相關文章:c語言教程

評論