一種基于ARM和FPGA的環形緩沖區接口設計

摘要:目前,基于ARM和FPGA架構的嵌入式系統在通信設備中得到廣泛的應用。文章提出了一種基于ARM和FPGA的環形緩沖區接口設計方案,從而實現了ARM和FPGA之間的數據緩沖和速率匹配。實際測試表明該方案能夠有效地對數據速率進行匹配,且具有良好的可擴展性。

關鍵詞:ARM;現場可編程門陣列;環形緩沖區

0 引言

隨著嵌入式系統、軟件無線電和無線通信的發展,基于嵌入式系統和軟件無線電的實現架構廣泛應用到無線通信設備中。其中,采用ARM+FPGA的軟件無線電體系結構來實現的通信設備是最近十分流行的一種方案。該方案充分利用ARM CPU靈活便捷的優勢,用來處理用戶輸入、系統控制、網絡協議功能,而利用FPGA卓越的實時信號處理優點,對無線通信的物理層信號進行無線收發處理。在這種體系結構中,ARM和FPGA的數據通信信號接口設計是其中十分關鍵的一個環節。由于無線設備的數據收發往往具有一定的突發性,在高速數據收發情況下,需要設計一種合理的緩沖區進行數據傳輸速率的匹配和緩沖。另外,對于ARM CPU來說,由于CPU往往需要同時并行處理多種任務,如何盡可能地保證數據的實時接收,也是設計中的一個關鍵。本文提出了一種基于ARM和FPGA的環形緩沖區設計結構,能可靠有效地處理好兩者之間數據傳輸速率匹配和緩沖,且具有很好的擴展性。

1 緩沖區接口硬件設計

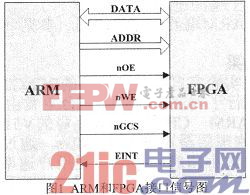

本方法設計的硬件接口如圖1所示。FPGA作為一個存儲器外設與ARM連接,采用的是標準的總線接口,由nGCS片選線、雙向數據線DATA、地址線ADDR、以及讀寫控制線nOE和nWE等信號線組成。另外,EINT是中斷信號線,FPGA發起中斷向ARM請求處理。

2 緩沖區接口軟件設計

為了設計ARM和FPGA的緩沖區接口,首先要利用圖1中的信號線實現ARM對FPGA的基本讀寫操作,這需要雙方遵循擬定的接口時序相互配合進行,這可以通過參考相應的ARM內核CPU用戶手冊,在FPGA端編寫相應的接口代碼來配合ARM CPU2端的讀寫時序實現。

下面重點介紹環形緩沖區接口的軟件實現。

2.1 緩沖區空間設計

如上所述,FPGA是作為ARM的一個存儲器外設來設計的。在本方案中,FPGA存儲器空間包括兩個部分:寄存器空間和數據緩沖區空間。

寄存器空間用于設置各種讀寫的參數,包括緩沖區讀寫指針、緩沖區忙閑狀態等;而緩沖區用于大量數據的臨時存儲,按作用分為發送緩沖區和接收緩沖區。設計中對所有空間都采用統一編址方式實現,利用ARM與FPGA之間相連的接口地址線(ADDR)的最高兩位來區分,例如,00表示寄存器空間,01表示發送緩沖區空間、10表示接收緩沖區空間,11為保留。

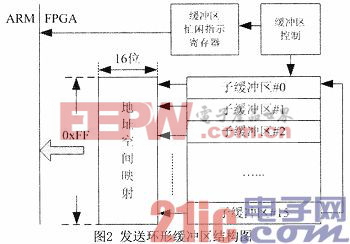

在本文的環形緩沖區結構設計中,發送(接收)緩沖區又分為若干大小相同的子緩沖空間,這些子緩沖空間共享同一個地址空間,由FPGA內部的緩沖區忙閑指示寄存器和子緩沖空間的控制指針來引導ARM對子緩沖區的讀寫。子緩沖空間的控制指針循環依次變化,數據幀也循環依次寫入指針指向的子緩沖空間或被讀走,這樣就構成了環形緩沖區。

以實際項目的設計為例,發送(接收)緩沖區分別由16個子緩沖空間組成,每個子緩沖空間的大小為256雙字節,這16個子緩沖空間共享一個地址空間。設計中的接口地址線一共為10位,數據線是16位。每個數據幀的最大長度也設置為256雙字節,以便一個緩沖區能夠裝滿一個幀,簡化緩沖區管理。以發送緩沖區為例,其結構設計如圖2所示。

盡管設置了16個子緩沖空間來應對可能的突發數據流,為了防止ARM將所有的子緩沖區寫溢出,在FPGA內部設置了緩沖區忙閑寄存器指示,當所有的子緩沖空間都寫滿后,緩沖區忙閑指示寄存器設置為忙。

fpga相關文章:fpga是什么

評論