ARM big.LITTLE系統技術應用

摘要:詳述了ARM首款big.LITTLE系統。利用完全一致的系統結合Cortex-A15以及Cortex-A7,因而在現有的高性能移動平臺以外開啟了全新的可能。

本文引用地址:http://www.j9360.com/article/147851.htm對于未來任何一種處理器,處理速度都將因為受限于散熱問題而無法大幅躍進。設備一旦達到熱障(thermal barrier)就會熔化,如果是移動電話,便會使設備的溫度上升造成用戶不適。除了物理層面的散熱問題外,能源效率也相當差。若調校處理器使其速度加快,則所需耗能便會呈指數數增長,而為了增加最后一丁點的性能需要付出的成本非常高。過去,尺寸倍增代表著速度翻倍,但如今,面積倍增,速度卻只增加幾個百分點,因此復雜度并不代表有效率,而這就是單一核心系統有所限制的原因之一。

如果無法加快單一核心的速度,那么就必須增加獨立核心的數量。這也有助于每個核心去應對其被分配到的任務需求,而這也就是ARM big.LITTLE(大小核)處理器技術的貢獻所在。

big.LITTLE處理器技術要解決業界目前最嚴峻的挑戰:通過提升性能和延長電池續航時間來拓展消費者“始終在線、始終連接”的互聯移動體驗。這種技術之所以能達成上述目標,是通過結合一個大(big)的多核心處理器與一個小(LITTLE)的多核心處理器,然后根據性能需求,以無縫的方式針對不同任務選擇合適的處理器。更重要的是這種動態選擇的動作,對于上層應用軟件或中間件在處理器上的執行絲毫沒有任何影響。

目前已應用于市面上移動設備的 的big.LITTLE設計,結合了高性能Cortex-A15多處理器集群與具有節能特色的Cortex-A7多處理器集群。這些處理器在架構上是百分之百兼容且具有相同功能(均支持LPAE、虛擬化擴充及NEON、VFP之類的運作單元),無須另外調整即可讓針對其中一種處理器類型所編譯的軟件應用程序順暢地應用于另一款處理器上。

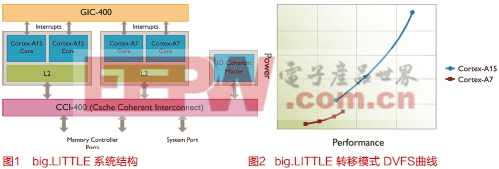

big.LITTLE 系統結構

就高速緩存一致性(cache coherency)的維護而言,無論是同一處理器集群中的高速緩存、或是跨不同處理器集的高速緩存,皆保持了高速緩存數據的一致性。這種跨集群的一致性來自ARM CoreLink高速緩存一致性互連(CCI-400,也能提供ARM Mali-T604之類的圖形處理器﹝GPU﹞系統等組件的I/O一致性)。兩種集群的中央處理器,還可通過CoreLink GIC-400之類的共享中斷控制器互傳信號。

big.LITTLE 系統執行模式

由于同一應用程序不需要任何修改就可以同時在Cortex-A7和Cortex-A15上運行,因此可以在隨機的情況下也能為某個應用程序選擇正確的處理器。下列執行模式便以此理論為基礎:

● big.LITTLE轉移模式;

● big.LITTLE MP模式。

顧名思義,轉移模式支持不同類型處理器之間的內容獲取和恢復。以中央處理器轉移來說,集群中每個中央處理器在另一個集群中都有對應的中央處理器,而軟件內容則以每個中央處理器為單位,隨機在不同的集群間轉移。如果集群中沒有正在運轉中的中央處理器,便可關閉整個集群以及相關的二級緩存(L2 cache)電源。MP模式則將軟件堆棧分配到兩個集群中各個處理器上。所有的中央處理器可同時運作,將系統性能提升到最高點。

big.LITTLE 轉移模式

轉移模式是動態電壓頻率調整(DVFS)等功耗/性能管理技術的延伸。轉移操作類似DVFS操作點的轉換。處理器上DVFS曲線的操作點,會隨負載變化不同而來回移動。在當前的處理器(或集群)已達到最高操作點時,如果軟件堆棧仍需要更高的性能,處理器(或集群)轉移就會發生。此時就會由另一個處理器(或集群)來執行工作,這個處理器(或集群)的操作點也會隨著負載變化不同而來回變動。當性能需求不再,可以再切換回之前的處理器(或集群)。

評論