富士通半導體交付55nm創新方案

近來中國IC市場的最重磅新聞要屬大小“M”——臺灣聯發科(MTK)和晨星半導體(MStar)宣布合并。“M兄弟”的聯手對已跨入“1億美元俱樂部”的少數剛崛起的大陸本土IC設計公司帶來很大的競爭壓力,而原本就缺資金、缺平臺、缺資源的本土小型和微型IC廠商的生存空間更加令人堪憂。

本文引用地址:http://www.j9360.com/article/134219.htm正如富士通半導體ASIC/COT業務市場部副經理劉哲女士在不久前閉幕的“2012深圳(國際)集成電路創新與應用展”(China IC Expo,簡稱CICE)“IC制造和設計”論壇上指出的,“現在中國的IC設計公司大概有300多家,營業額在10M美金以上的可能不到10%,在100M美金以上的可能不到10家,總體來講中國IC設計產業還不是很健全,同質競爭嚴重,缺乏創新。我研究了一下過去5年中統計的中國十大公司,發現5年都能上榜的大概只有5家,市場的優勝劣汰十分激烈。”

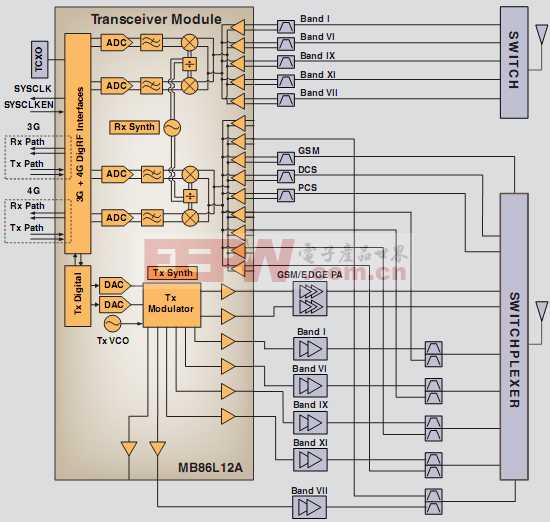

那么本土IC設計業如何能夠更好地在市場立足,在如此激烈的競爭中生存,并且不斷的壯大自己?劉哲及富士通半導體IP平臺解決方案事業部副總經理安佛英明先生針對這個話題在論壇做了題為“富士通半導體SoC 設計和芯片代工解決方案”的演講,分析了目前中國本土IC設計業在SoC設計中所面臨的挑戰和應對方法,并宣布了富士通半導體為中小型IC設計公司量身定制的55nm最新設計和制造服務解決方案從7月開始提供PDK和library給客戶進行設計。

SoC設計挑戰分析

“目前業界在SoC設計上遇到的挑戰最關鍵有兩點:一是Time-to-Market,二是cost。迎接這個挑戰就要從——工藝制程(Process)、IP、設計三個方面下工夫。選擇正確的工藝,有競爭力的IP及先進的設計方法是SoC成功的關鍵。” 劉哲簡潔明了地概括了SoC設計的成功之道。

圖1:SoC設計遇到的挑戰。

她特別強調了所謂正確的工藝制程并不是指最先進的工藝制程,而是最有性價比的,符合中國本土IC公司承受能力的,既能夠保證產品上市時間又降低成本的合適工藝制程。那么到底什么才是中國本土IC設計真正需要的工藝制程呢?

55nm——中國IC設計真正之“渴”

如今的消費類電子市場競爭已經進入白熱化階段,客戶的需求、競爭對手的挑戰都使得中國本土IC設計公司面臨巨大的生存壓力。另一方面,摩爾定律面臨極限挑戰,高端工藝因其高昂的前期投入成為中小設計公司可望而不可即的奢侈品。此外,低功耗的要求促使芯片設計者不得不追逐最新的40nm和28nm工藝,但這意味著巨大的風險和投入,無論是工藝還是IP的投入和成熟度都在一定程度上阻礙了許多想法最終轉變成硅片。

從2010年開始,中國開始出現越來越多的40nm設計,其中不乏幾千萬門級的智能終端IC。但40nm工藝超過百萬美元的一次NRE費用著實讓中國本土IC公司“傷不起”,加上IP方面不菲的投資以及整合驗證,使得項目風險很大。

如何以更低的投入最大化地利用主流的且成熟的65nm工藝去設計產品是業界很多公司都在尋求的目標。本次展會上,富士通半導體ASIC/COT業務部最新推出的兩套創新的55nm工藝制程CS250L和CS250S引起與會業內人士的高度關注,他們可幫助中國便攜消費類終端IC設計公司以65nm的成本水平實現功耗大幅降低、性能堪比40nm工藝的設計,對成本、上市時間和功耗極其敏感的消費終端ASIC設計意義重大。

圖2:富士通半導體ASIC/COT業務部攜55nm創新工藝隆重登場2012 CICE。

評論