先柵極還是后柵極 業界爭論高K技術

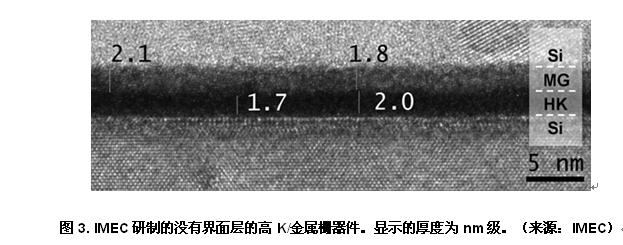

消除SiO2界面層方面,在去年12月份舉辦的IEDM會議上,科學家們發布了多篇有關如何消除SiO2界面層的文章(ZIL:zero interface layer),其中IBM的Fishkill技術聯盟也公布了自己的方案,并宣稱這種方案將在自己的gate-first 32/28nm制程中使用。(圖3)

本文引用地址:http://www.j9360.com/article/111062.htm

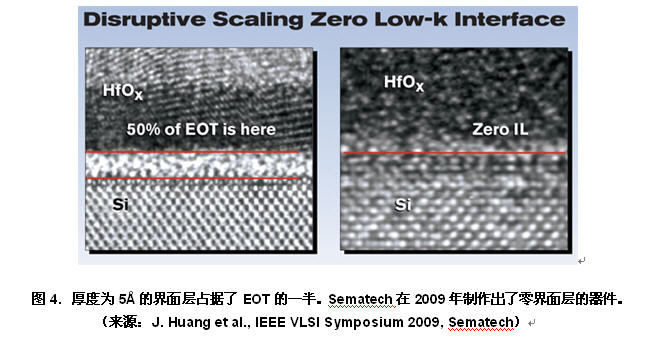

耶魯大學的T.P. Ma教授表示,ZIL技術雖然非常吸引人,但通常需要使用高溫工步來消除SiO2界面層,而gate-first工藝制作的柵極則正好能夠承受這種高溫,所以這項技術對采用gate-first工藝的廠商比較有利。他認為,按照他的理解,ZIL技術的實現需要使用“高溫化學反應”來有效地去除柵極結構中殘留的SiO2界面層,這樣這項工藝對使用gate-first工藝的廠家而言實現起來難度更小一些,而使用gate-last工藝的廠商則會盡量避免使用高溫工步。他還表示,IBM和Sematech公司所制出的ZIL結構已經能夠在5埃的等效氧化層厚度條件下達到較好的防漏電性能。

不過據Sematech公司的材料與新興科技研發副總裁Raj Jammy表示,盡管Sematech公司早期的ZIL結構確實是在gatefirst工藝的基礎上制造出來的,但是“要制出ZIL未必需要依靠高溫處理工步,而主要是要去掉界面層中的氧離子。”他還強調不同的情況需要采用不同的熱處理方式來進行處理,才能得到較好的管子參數。(圖4)

另外一篇IMEC的研究報告則指出,“我們制作ZIF的方法是需要進行高溫熱處理的,不過要生成理想的無界面層柵極結構的方法有很多種,因此未必說gatelast工藝就不利于ZIL的制作。”他還表示應該可以找到一種方案來兼顧ZIL與gatelast工藝的優點。

另外,在被問及對ZIL技術的看法時,Intel高管Bohr回答稱,“在我的印象中這種技術并不是很有效,這主要是由于ZIL結構對溝道的載流子遷移率有一定的不良影響,而如果我們能夠很好地控制界面層的材料和厚度,管子的性能一樣也可以達到要求”,他還表示“相比之下,我認為我們應該努力去改善High-K絕緣層的材料,并想辦法減小金屬電極的電容.”

Gartner 市調公司的Freeman則表示,從28nm制程節點開始,臺積電公司與GlobalFoundries之間的HKMG產品由于所用的工藝不同,因此將存在比較明顯的區別。按照這樣的差別趨勢發展下去,一種最終的可能就是IBM和GlobalFoundries會在22nm制程節點馬上轉向gate- last工藝,而另外一種可能就是由于gatefirst在ZIL方面的優勢被實際的應用證明,而將慢慢處于領先的位置。Freeman還表示:“在 16nm制程節點,如何控制好管子的界面層,將是至關重要的。”

參考文獻:

1. J. Markoff, "Intel Says Chips Will Run Faster, Using Less Power," New York Times, Jan. 27, 2007, p. 1.

2. D. Lammers, "Pressure Builds on Gate-First High-k," Semiconductor.net, Dec. 9, 2009.

3. D. Lammers, "GlobalFoundries Adds Qualcomm, Supports Gate-First Technology at 28 nm Generation," Semiconductor.net, Jan. 7, 2010.

4. G.H. Ma, et al., "A Novel ‘Hybrid' High-k/Metal Gate Process for 28 nm High Performance CMOSFETs," 2009 IEDM, p. 655.

5. T. Hoffmann, "High-k/Metal Gates: Industry Status and Future Direction," 2009 IEDM Short Course.

6. C.H. Jan et al., "A 32 nm SoC Platform Technology With 2nd Generation High-k/Metal Gate Transistors," 2009 IEDM, p. 647.

7. J. Huang et al., "Gate First High-k/Metal Gate Stacks With Zero SiOx Interface Achieving EOT=0.59 nm for 16nm Application," 2009 Symposium on VLSI Technology.

8. T. Ando, et al., "Understanding Mobility Mechanisms in Extremely Scaled HfO2 (EOT 0.42 nm) Using Remote Interfacial Layer Scavenging Technique and Vt-tuning Dipoles With Gate-First Process," 2009 IEDM, p. 423.

評論