先柵極還是后柵極 業界爭論高K技術

Pellerin 強調:“我們肯定會在28nm節點制程上使用Gate-first工藝。其原因是我們的客戶希望在轉換到HKMG結構時能夠盡量避免過多的設計變更。”

本文引用地址:http://www.j9360.com/article/111062.htm臺積電的技術高管蔣尚義則表示,類似的難題業界在20年前便曾經經歷過:“當時業界同樣曾經發現N+摻雜的PMOS柵極材料會造成Vt電壓較高,這樣業內一些公司便開始向溝道中摻雜雜質以壓低Vt,結果卻帶來了很多副作用,比如造成短通道效應更為明顯等等。”而目前使用Gate-first工藝制作HKMG晶體管的方案的情況則與此非常類似,盡管人們可以采用加入上覆層等方式來改善Gate-first工藝容易造成Vt過高的問題,但是加入上覆層的工藝卻非常復雜和難于掌握。因此臺積電干脆選擇轉向Gate-last工藝,不過Gate-last工藝實施時如果想保持與Gate-first工藝產品的管芯密度近似,需要設計方對電路Layout進行重新設計。

Gartner公司的半導體產業分析師Dean Freeman表示:“臺積電轉向Gate-last,說明這種工藝在性能方面還是存在一定的優越性的。雖然Gate-first工藝制成的產品在管芯密度方面 較有優勢,但繼續應用這種工藝一定存在一些臺積電無法克服的難題。”

IMEC負責high-k技術研發的主管Thomas Hoffmann曾經在IEDM2009大會上指出了Gate-first工藝在性能方面存在的不足,不過在會后的一次訪談中,他表示盡管Gate- first存在一些性能方面的缺點,但是對一部分對性能并不十分敏感的第功耗器件還是能夠滿足要求的。

他表示:“對瑞薩等開發低功耗器件的公司而言,也許Gate-first工藝是目前較好的選擇。這類器件一般對Vt值和管子的性能并沒有太高的要求。不過當產品的制程節點發展到28nm以上級別時,這些公司便需要轉向Gate-last。”

不過”對以追求性能為主的廠商而言,Gate-last則是必然之選。IBM的產品顯然屬于這種類型,所以我認為如果他們不使用Gate-last的話,就必須在如何降低Vt的問題上想出好辦法。當然這種方案的復雜性會更大,而且還有可能會影響到產品的良率。而最終他們也有可能會倒向Gate-last工藝,這就是IBM Fishkill生產技術聯盟中的伙伴感到擔心的地方。“

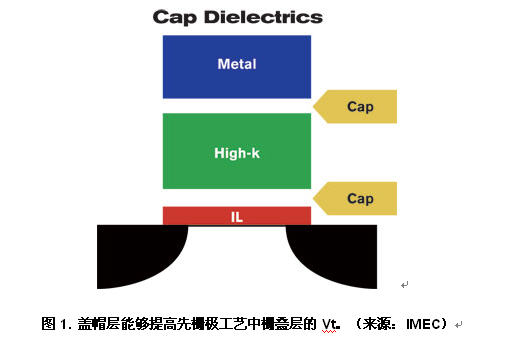

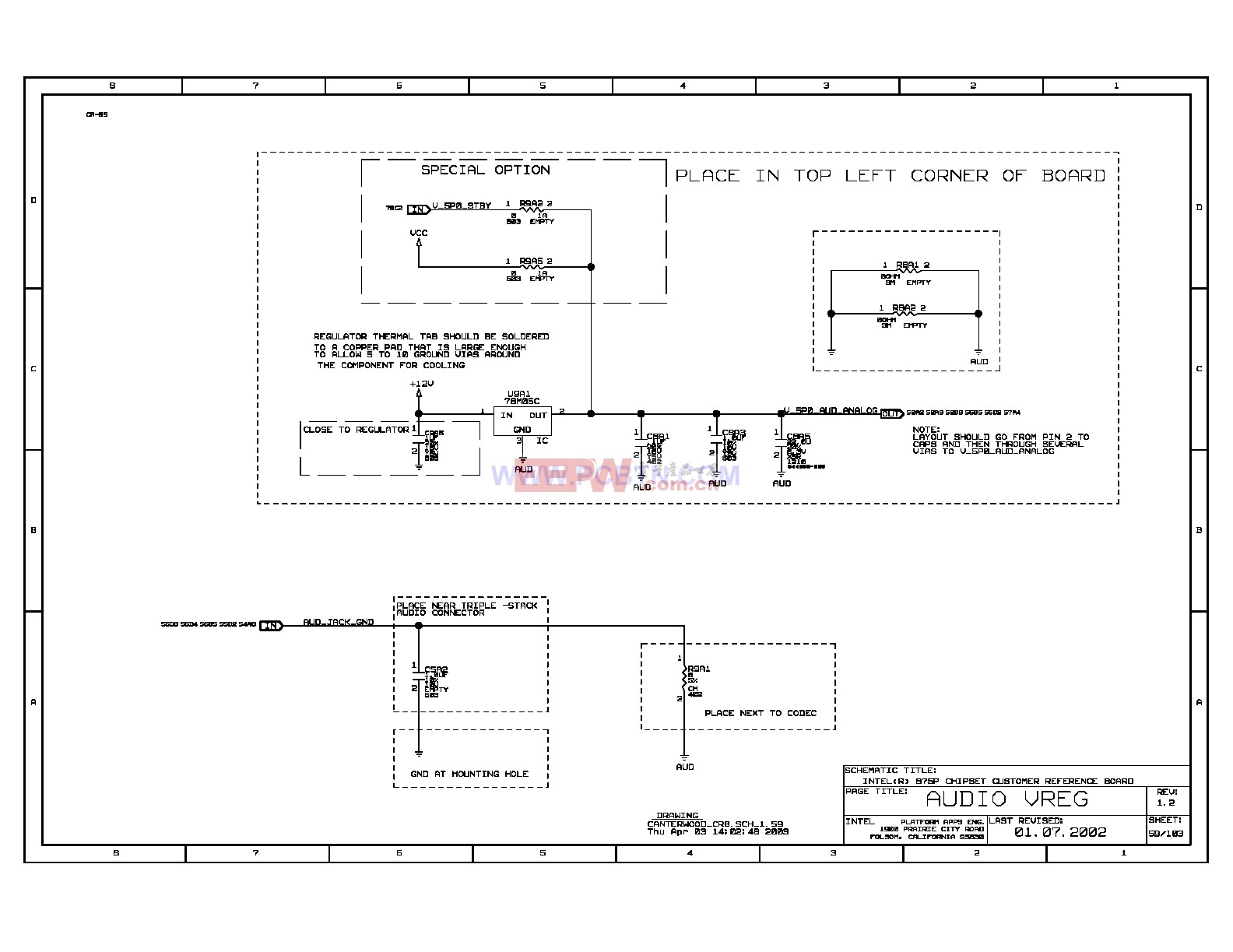

據Hoffmann介紹,盡管在Gate-last工藝中,制造商在蝕刻和化學拋光(CMP)工步會遇到一些難題,但是Gate-first工藝也并非省油的燈。如前所述,目前Gate-first工藝雖然不好控制Vt,但也不是完全沒有辦法,其主要的手段是通過設置 一定厚度的high-k絕緣體上覆層(cap layer)來實現,這種方案需要在high-k層的上下位置沉積氧化物薄層。比如在NMOS管中,便需要在high-k層的上部沉積一層厚度小于1nm的 La2O3薄層,以達到調整Vt電壓的目的;而在PMOS管中,則需要通過蝕刻工步將這一層薄層去掉,換成 Al2O3材質的薄層,這樣便需要復雜的工藝來控制如何在PMOS管中將這一薄層去掉而不影響到NMOS的上覆層。PMOS器件上Al2O3蓋帽層被用來控制Vt(圖1)。

他表示:”NMOS管的上覆層需要采用La2O3材料制作,而PMOS管則需要用Al2O3來制作上覆層,這樣就需要在NMOS管的上覆層上覆蓋一層光阻膠,然后再用顯影+蝕刻方式去掉沉積在PMOS管中的La2O3,不過處理完成之后要除去覆蓋在厚度小于1nm的La2O3 上覆層上的光阻膠時,由于上覆層的厚度極薄,因此如果不能小心控制就會對上覆層造成一定的損壞,這就要求廠商具備非常高超精密的去膠工藝。“

ASM公司的外延產品和ALD(原子層淀積)業務部經理Glen Wilk則表示業內已經就gate-first與gate-last之間在性能,復雜程度和成本方面的優劣對比爭執了許久,”不過我認為隨著產品制程尺寸的進一步縮小,gate-last工藝的優越性開始逐步體現,由于這種工藝的柵極不必經受高溫工步,因此廠商可以更加自由地設置和調配柵電極材料的功函數值,并很好地控制住管子的Vt電壓。”

評論