先柵極還是后柵極 業界爭論高K技術

Wilk表示,隨著制程尺寸的進一步縮小,采用 gate-first工藝的廠商會發現“PMOS管的特性越來越難控制,實施Gate-first工藝的難度也悅來越大,因此我認為未來業界對gate- last工藝的關注程度會越來越廣泛。”Wilk認為,由于gate-last工藝可以很好地控制柵極材料的功函數,而且還能為PMOS管的溝道提供有利改善溝道載流子流動性的硅應變力,因此gate-last工藝將非常適合低功耗,高性能產品使用,他表示:“不過我認為內存芯片廠商可能在轉向gate-last工藝時的步伐可能會稍慢一些,他們可能會在未來一段時間內繼續使用gate- first工藝,不過gate-last工藝顯然有助于提升產品的性能和降低產品的待機功耗。”

本文引用地址:http://www.j9360.com/article/111062.htmApplied Materials公司的CTO Hans Stork則表示gate-first工藝需要小心對待用來控制Vt電壓的上覆層的蝕刻工步,而gate-last工藝則需要在金屬淀積和化學拋光工步加以注意。“長遠地看,我認為Gate-last工藝的前景更好一些。”他表示芯片廠商目前都非常關注Intel 公司的32nm制程SOC芯片工藝,在這種工藝中,high-k絕緣層的等效氧化物厚度(EOT)為0.95nm.他說:“Intel將其32nm gate-last制程SOC芯片產品的應用范圍從高性能應用市場進一步拓展到了低漏電/低電壓應用領域,而手機芯片則正好需要具備這些特性。”客戶們對 gate-last和gate-first工藝在工函數控制,成本,產能,良品率等方面的實際對比數據非常關注。以至于已經有部分手機芯片廠商如高通等已經開始要求代工商能為他們提供“能與Intel的產品性能相近”的產品。

在IEDM2009 會議上,高通公司的高管曾表示他們很支持臺積電去年七月份宣布將啟用Gate-last工藝的決定。而今年1月份,高通則宣布已經與 GlobalFoundries公司簽訂了28nm制程產品的代工協議。這樣,屆時人們便有機會可以實際對比一下分別來自臺積電和 GlobalFoundries兩家公司,分別使用gate-last與gate-first兩種工藝制作出的手機芯片產品在性能方面究竟有多大的區別。目前,高通公司的40nm制程手機用處理器類屬與高性能芯片,其運行頻率達到了1GHz,不過其功耗也控制得相當好,在谷歌Android智能手機中有使用這種處理器產品。

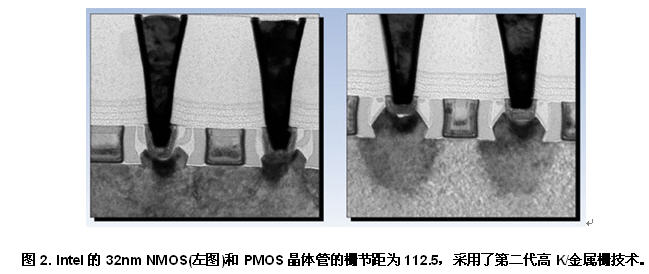

Intel公司的制程技術高管Mark Bohr則表示Intel公司的Atom SOC芯片還需要一年左右的時間才會啟用32nm制程工藝(圖2)。當被問及應用gate-last工藝以后為什么芯片的核心尺寸會有所增大,是不是由于 gate-last本身的限制,導致更改后的電路設計方案管芯密度有所下降的問題時,Bohr表示Intel公司45nm gate-last HKMG制程產品上電路設計方案的變動并不是由于應用了gate-last所導致,而是與當時Intel在45nm制程產品上還在繼續使用干式光刻技術有關。他表示“當時之所以會采用那種核心面積較大的設計規則,其目的并不是為了滿足Gate-last HKMG工藝的要求,而是要滿足使用干式光刻技術的要求。”

零界面層

High-k絕緣層的材料選擇方面,包括Intel公司的Bohr在內,大家似乎都同意HfO2將在未來一段時間內繼續被用作High-K層的材料,業界近期將繼續在改良HfO2材料上做文章,部分廠商可能還會考慮往HfO2層中添加一些特殊的材料,但他們近期不會把主要的精力放在開發介電常數更高的材料方面。

另外,有部分廠商的主要精力則會放在如何減小High-k層下面的SiO2界面層(IL)的厚度方面,其目標是在High-k絕緣層的等效氧化物厚度為10埃時能把這種界面層的厚度降低到5埃左右。Sematech公司負責High-k項目研究的高管Paul Kirsch表示:“業內現在考慮較多的主要是如何進一步優化HfO2材料,而不是再花上五年去開發一種新的High-k材料。從開發時間要求和有效性要求方面考慮,目前最有意義的思路是考慮如何消除SiO2界面層和改善High-K絕緣層的介電常數值。”

評論