基于Taylor級數近似補償的改進數控振蕩器實現

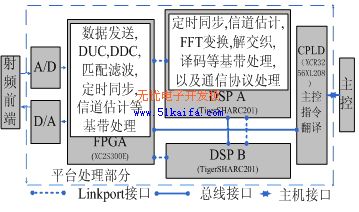

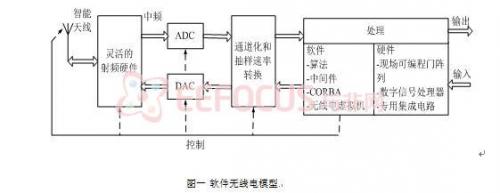

基于本文設計結構的改進數控振蕩器采用了Verilog HDL進行實現,并在Altera公司CycloneⅡ系列的FPGA上進行了綜合、布局布線和驗證,本設計也在國家“863”項目“軟硬件可重構的新一代無線通信統一平臺研究”中得到應用,在速度和精度上都能很好的滿足平臺的需要。

結語

本文提出一種適用于軟件無線電通信系統的數控振蕩器實現新方法,該方法利用流水線CORDIC結構來實現數控振蕩器,這樣可以實現高速的數控振蕩器;同時,該方法采用殘余相角補償、二階泰勒(Taylor)級數近似、相位抖動等措施來補償CORDIC在精度方面的不足,使數控振蕩器的SFDR值得到了很大的提高。該方法實現的數控振蕩器能滿足軟件無線通信系統的速度和精度的要求,并且也成功應用在軟件無線電平臺上,表現出很好的性能。

參考文獻:

[1] Volder,Jack E.The CORDIC trigonometric computing technique [J]. IEEE Transactions on Electronic Computers,1959;EC-8:330-334

[2] Hu Y H.The quantization effects of the CORDIC algorithm [J]. IEEE Transactions on Signal Processing,1992;40(4):834-844

[3] 張科峰,彭帥,蔡夢. 基于CORDIC算法的NCO [J]. 現代雷達,2008;30(6):91-94

[4] Sodagar A.M.,Lahiji G.R. A pipelined ROM-less architecture for sine-output direct digital frequency synthesizers using the second-order parabolic approximation [J]. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing,2001;48(9):850-857

[5] Wang W,Zeng Y.F,Yan Y. Efficient wireless Digital Up Converters design using system generator [J]. International conference on Signal Processing,2008;ICSP 2008:443-446

[6] Madisetti A,Kwentus A.Y,Wilsson A.N. Jr. A 100-MHz, 16-b, direct digital frequency synthesizer with a 100-dBc spurious-free dynamic range [J]. IEEE Journal of Solid-State Circuits,1999;34(8):1034-1043

評論