利用低端柵極驅動器IC進行系統開發

低端柵極驅動器IC是專用放大器,普遍用于電源設計中,根據來自PWM控制器的輸入信號開關接地參考MOSFET和 IGBT。對于低于100~200W的低功率轉換器,這些驅動器可以成功地集成到PWM控制器中以減少元件數,只要滿足一定條件便沒有問題。這些條件包括:MOSFET開關速度足夠快,讓開關損耗在可接受的范圍內;較高驅動電流脈沖產生的噪聲不會干擾控制功能;以及PWM IC的板上散熱易于管理。另一方面,在較高功率的轉換器中,一般采用單獨的驅動器IC以提供更大的驅動功率或更方便地管理噪聲和散熱。此外,通過對控制器采用更低的電源電壓,以及采用較高電壓來驅動功率開關,可以提高電源效率,而柵極驅動器IC能夠很好地完成這種電平轉換工作。

本文引用地址:http://www.j9360.com/article/101082.htm為節約成本,有時也采用分立式元件來搭建簡單的柵極驅動電路,在不需要具有先進功能及性能的驅動器IC時,這樣做是可行的。不過,這種方案有不少局限性。例如,如果選定NPN/PNP射極跟隨器的輸出級,偏置電路的設計就必須謹慎,當晶體管的輸出飽和電壓高至快速開關電壓時,會致使輸出電壓的擺幅減小。如果在輸出端改用PMOS/NMOS反向器,控制邏輯必須適應這種邏輯轉換,而且當驅動器改變狀態時一般有部分擊穿。利用上述兩種技術的任一種,這種低增益級都需要輸入快速邊緣來產生快速的切換,需要更多的電路來執行電壓級轉換等功能,而元件數的增加對空間、裝配時間及可靠性都有不良影響。

柵極驅動器IC能夠解決上述大部分問題。它們集成有使能和欠壓鎖定(UVLO)等功能,可以輕松地在啟動、關斷和發生故障等最棘手的工作條件下控制功率開關。很小的邏輯門就能夠很容易地驅動高阻抗輸入,而且由于驅動器IC包含有帶正反饋的高增益電路,故只要輸入電壓超過閾值,輸出總是能夠快速切換。當IC需要設計以防止閾值電壓隨過熱波動時,很容易通過在輸入端添加簡單的RC電路來插入一個固定延時。

驅動器大小的決定

使用低端驅動器的兩類常見開關是具有硬開關拓撲的初級端開關特征的鉗位感應開關,以及同步整流。決定驅動器大小的標準各不相同,這里做一個檢閱。

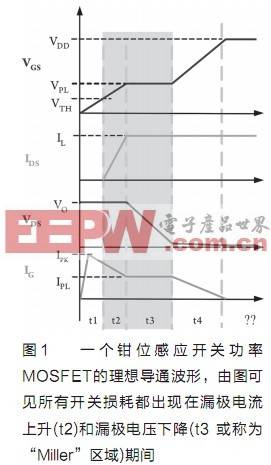

圖1所示為鉗位感應開關的理想導通波形,其特征是漏源電流的上升和漏源電壓的下降之間沒有重疊。這產生最差情況的開關損耗,通常表示為整個轉換器開關時間TS上的平均功耗,即使實際功耗只發生在圖中的t2和t3上。

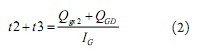

(t2+t3)的長度取決于平均柵極驅動電流IG和MOSFET柵極穿越這些時間間隔所必需的電荷量,兩者都可以在 MOSFET規格中找到,或者是從總柵極電荷曲線上讀取。

關斷波形是圖1的鏡像圖形,可以采用類似的方法計算關斷開關損耗,并代入式(1),求出該功率開關的總開關損耗。從這些式子可明顯看出,在損耗時間間隔內,開關損耗與柵極驅動電流成反比。對于鉗位感應開關,開關損耗是決定柵極驅動器大小的主要指標。事實上,當它的輸出電壓接近工作范圍中間值時,最重要的驅動器特性是其輸出電流。

評論