國產256核RISC-V處理器曝光,計劃擴展到1600核!

隨著每一代新一代芯片增加晶體管密度變得越來越困難,因此芯片制造商正在尋找其他方法來提高處理器的性能,其中包括架構創新、更大的芯片尺寸、多芯片設計,甚至晶圓級芯片,比如 Cerebras的WSE系列AI芯片。

近日,中國科學院計算技術研究所的科學家們也推出了一款先進基于RISC-V架構的 256 核多芯片,并計劃將該設計擴展到 1,600 核,以創造整個晶圓大小的芯片,以作為一個計算設備。

據 The Next Platform報道,中國科學院計算技術研究所的科學家在《基礎研究》雜志最近發表的一篇文章中介紹了一種先進的 256 核多芯片計算復合體,名為“浙江大芯片”。

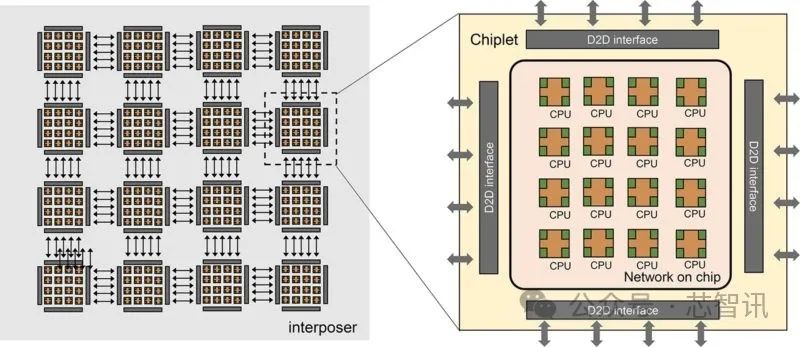

據介紹,該芯片設計由 16 個小芯片組成,每個小芯片包含 16 個 RISC-V 內核,并使用片上網絡以傳統的對稱多處理器 (SMP) 方式相互連接,以便小芯片可以共享內存。每個小芯片都有多個芯片到芯片接口,可通過 2.5D 中介層連接到相鄰的小芯片,研究人員表示,該設計可擴展到 100 個小芯片,或 1,600 個內核。

據報道,“浙江大芯片”基于Chiplet架構設計,采用 22 納米級工藝技術制造,目前還不確定使用中介層互連并在 22 納米生產節點上制造的 1,600 個核心組件會消耗多少功率。不過,由于延遲的減少,這將極大地優化其功耗和性能。

論文探討了光刻和Chiplet技術的局限性,并討論了這種新架構滿足未來計算需求的潛力。研究人員指出,多芯片設計可用于構建百億億次超級計算機的處理器,AMD 和英特爾目前正在做這件事。

研究人員寫道:“對于當前和未來的百億億次計算,我們預測分層chiplet架構將是一種強大而靈活的解決方案。” “分層chiplet架構被設計為具有多個內核和許多具有分層互連的小芯片。在chiplet內部,內核使用超低延遲互連進行通信,而小芯片之間則以受益于先進封裝技術的低延遲互連,從而可以最大限度地減少這種高可擴展性系統中的小芯片延遲和NUMA效應”。

與此同時,研究人員建議對此類組件使用多級內存層次結構,這可能會給此類設備的編程帶來困難。

“內存層次結構包含核心內存[緩存]、芯片內內存和芯片外內存,”描述中寫道。“這三個級別的內存在內存帶寬、延遲、功耗和成本方面有所不同。在分層chiplet架構的概述中,多個核心通過交叉交換機連接并共享緩存。這形成了pod結構,并且pod通過chiplet內網絡互連,多個pod組成一個chiplet,chiplet通過chiplet間網絡互連,然后連接到片外存儲器,需要仔細設計才能充分利用這種層次結構合理利用內存帶寬來平衡不同計算層次的工作量可以顯著提高chiplet系統效率。正確設計通信網絡資源可以保證chiplet協同執行共享內存任務。

大芯片設計還可以利用光電計算、近內存計算和 3D 堆棧內存等技術。然而,論文沒有提供這些技術實施的具體細節,也沒有解決它們在設計和構建此類復雜系統時可能帶來的挑戰。

來源:芯智訊

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。