一文搞懂SiC功率器件的市場、應用和制造工藝

報告主題:一文搞懂SiC功率器件的市場、應用和制造

報告作者:Dr. Victor Veliadis

Deputy Executive Director and CTO, PowerAmerica

Professor ECE North Carolina State University, Raleigh, NC USA

報告內容包含:(具體內容詳見下方全部報告內容)

SiC/GaN 性能科普

Si、SiC 或 GaN 的選擇應用差異

汽車電氣化是寬禁帶(WBG功率器件和電子裝置的一大機遇

SiC功率器件的制造

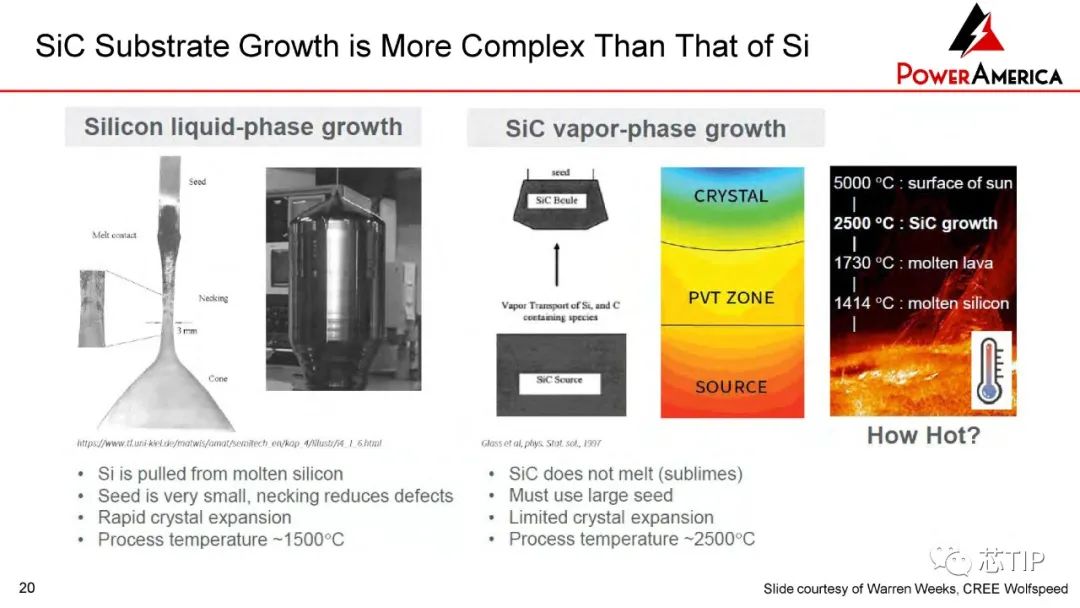

SiC襯底的生長比Si更復雜

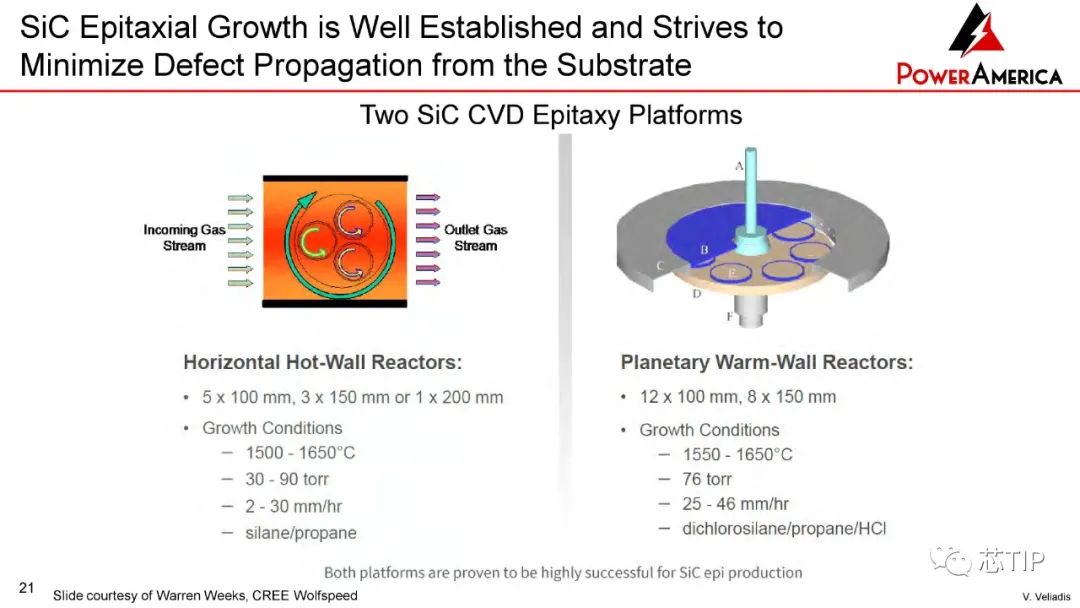

SiC外延技術成熟度相對較高

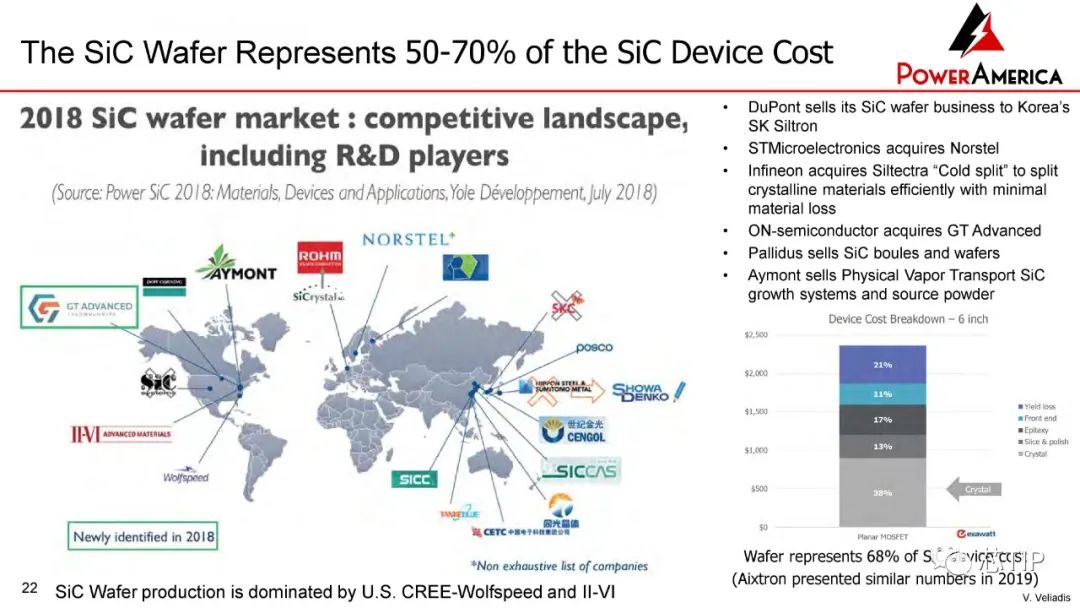

SiC 晶圓占 SiC 器件成本的 50-70%

高壓 (+900 V) SiC 功率器件通常采用縱向配置

SiC 器件的理想阻斷電壓由其漂移層的厚度和摻雜決定

電壓和開關頻率需求推動單極與雙極 SiC 器件的選擇

SiC制造需要投資特定的設備和開發特定的工藝

...

報告詳細內容

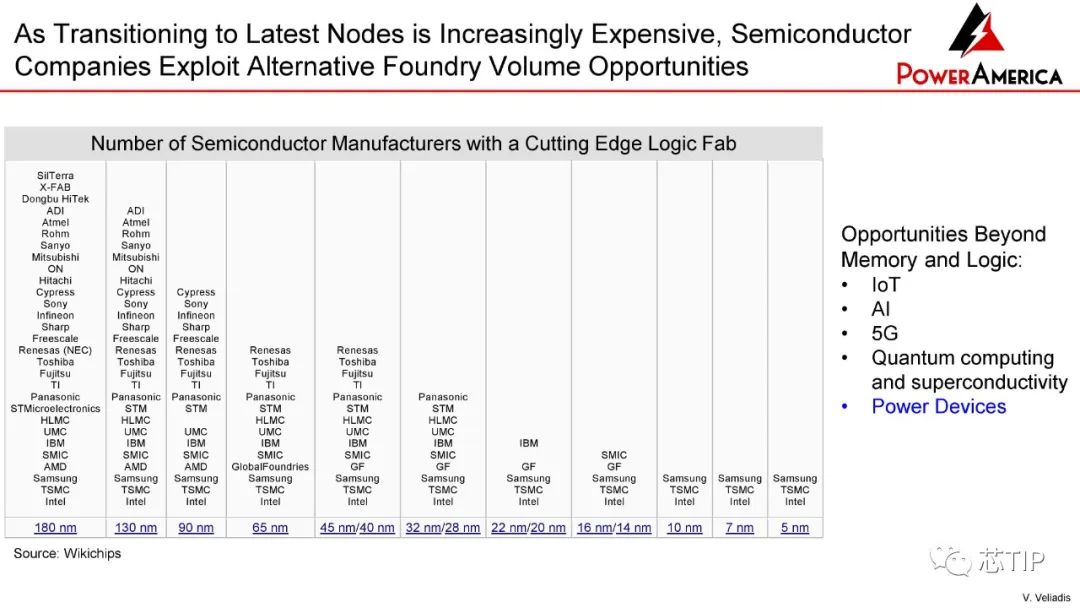

# 各節點的半導體制造商數量

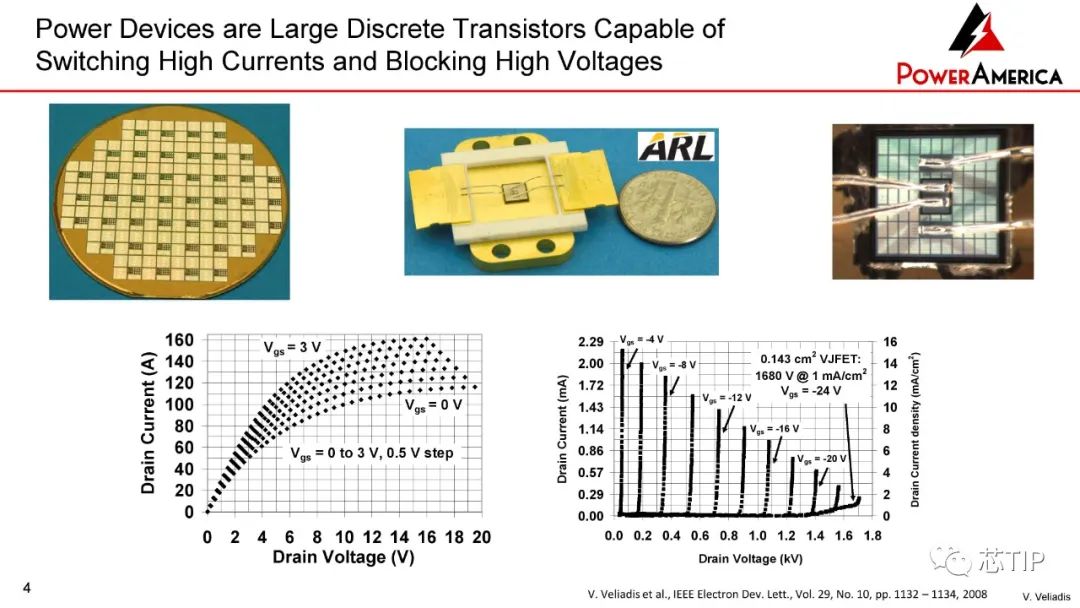

# 功率器件是能夠切換高電流和阻斷高電壓的大型分立晶體管

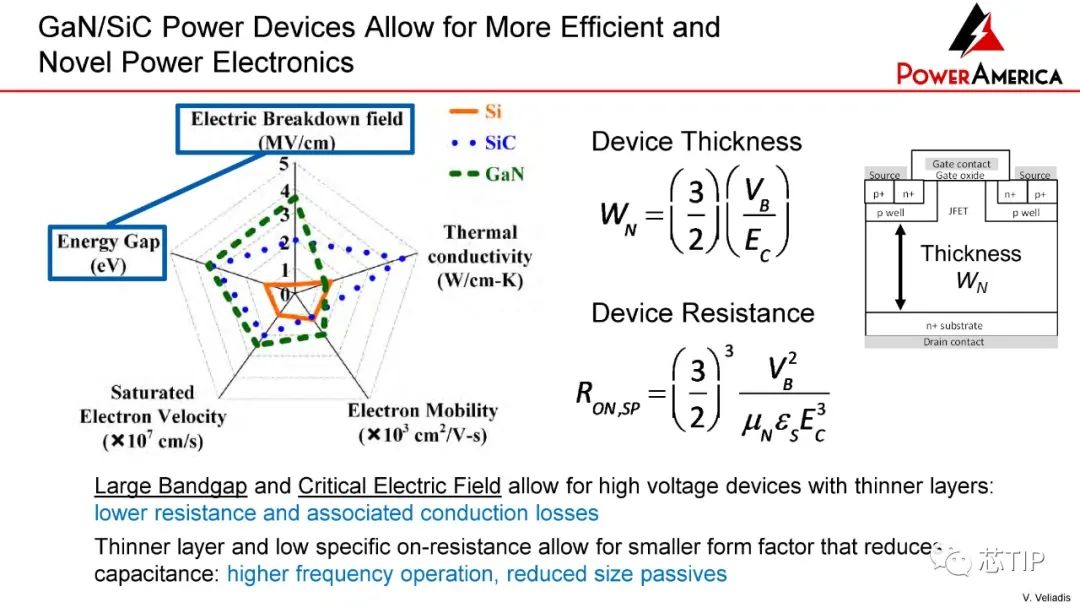

# GaN/SiC 功率器件可實現更高效、更新穎的電力電子設備

(更低的電阻和相關的傳導損耗;更高頻率的操作、更小的器件尺寸)

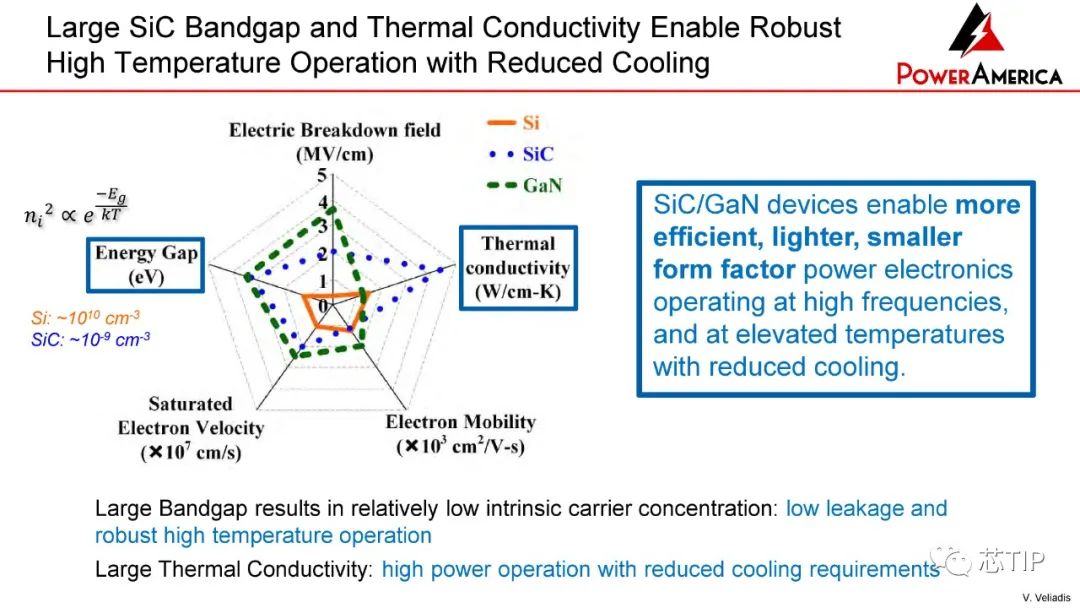

# SiC/GaN 器件可實現更高效、更輕、更小尺寸的電力電子設備

(可在高頻和高溫下運行,同時減少冷卻)

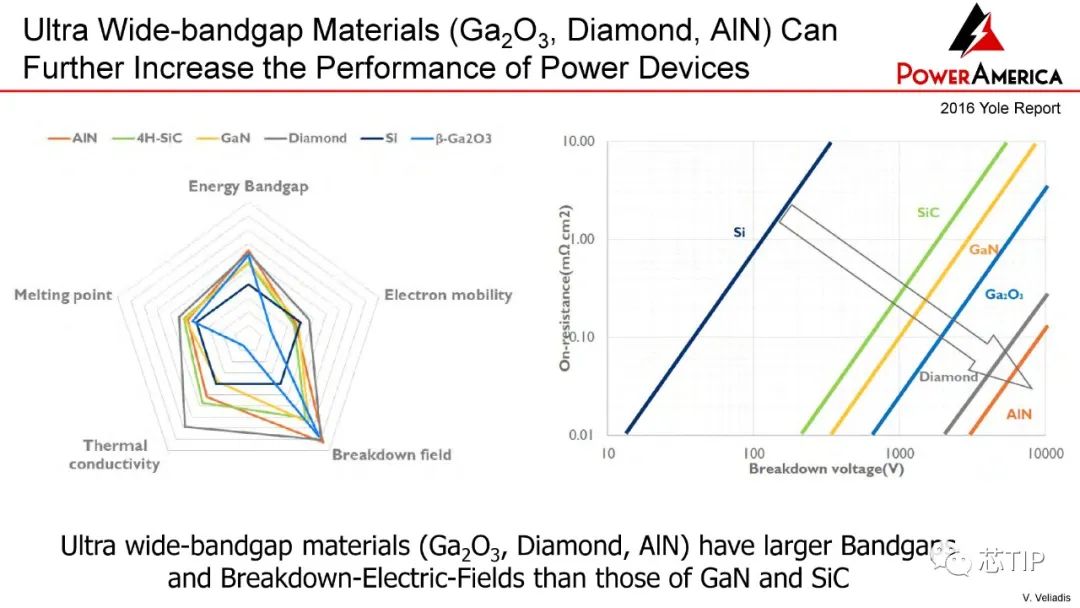

# 超寬帶隙材料(Ga2O3、金剛石、AlN)可以進一步提高功率器件的性能

(超寬帶隙材料(Ga2O3、金剛石、AlN)具有比 GaN 和 SiC 更大的帶隙和擊穿電場)

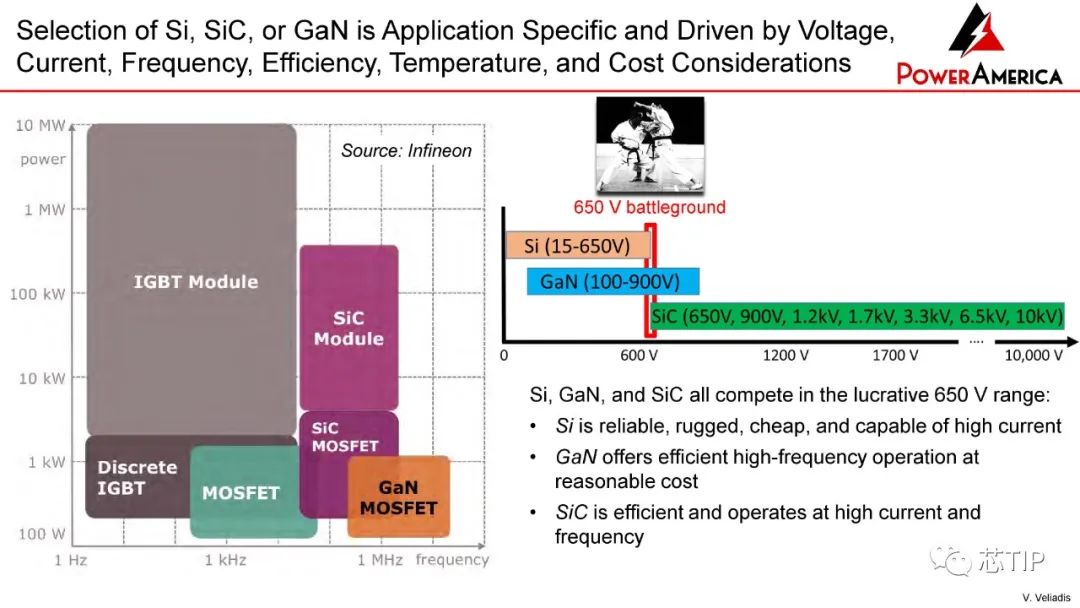

# Si、SiC 或 GaN 的選擇因應用而異,并受電壓、電流、頻率、效率、溫度和成本考慮因素驅動

Si、GaN 和 SiC 都在 650 V 范圍內展開競爭:

? Si 可靠、堅固、便宜且能夠承受大電流

? GaN 以合理的成本提供高效的高頻操作

? SiC 效率高,可在高電流和高頻率下運行

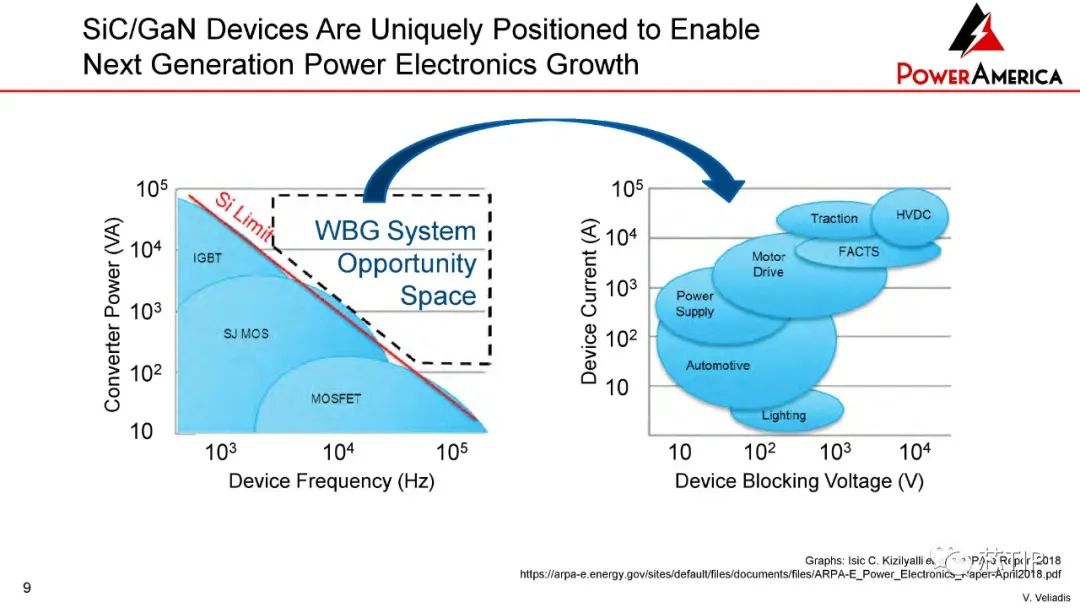

# SiC/GaN 器件在實現下一代電力電子增長方面具有獨特優勢

# 寬禁帶(WBG)電力電子是高價值制造產品的關鍵驅動力

(汽車、IT硬件、電網、電機驅動、航空航天部門等)

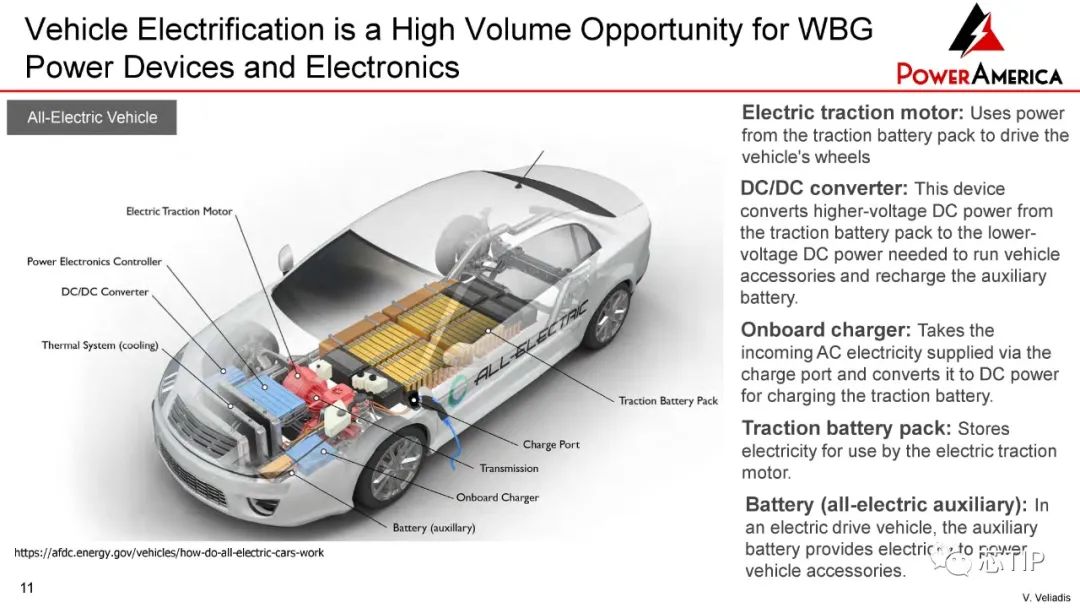

# 汽車電氣化是寬禁帶(WBG功率器件和電子裝置的一大機遇

(電機、DC/DC轉換器、車載充電器、動力電池組、蓄電池輔助裝置等)

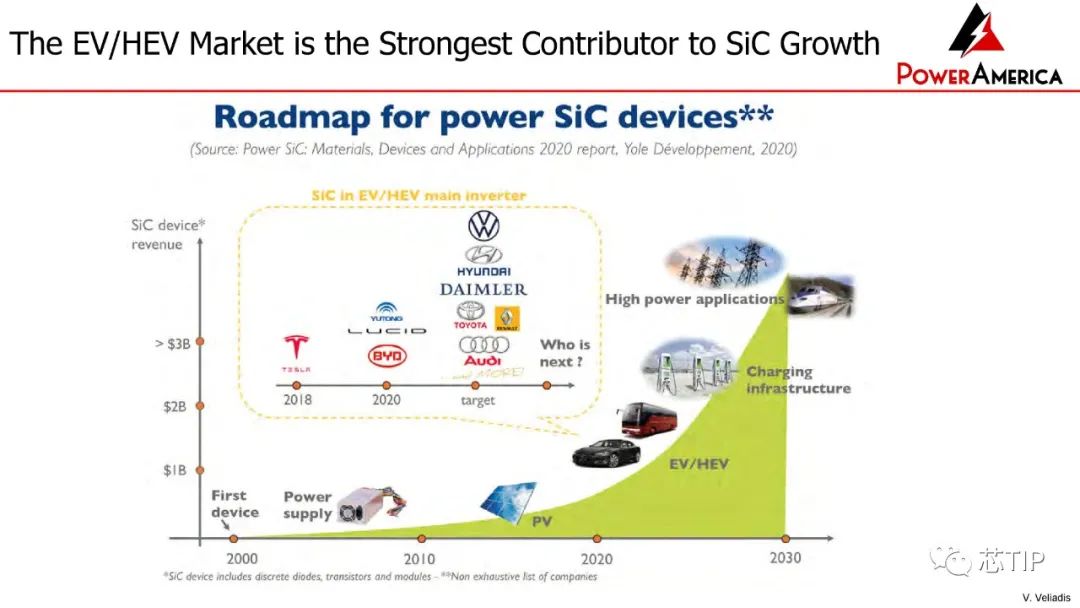

# EV/HEV 市場是 SiC 增長最強勁的貢獻者

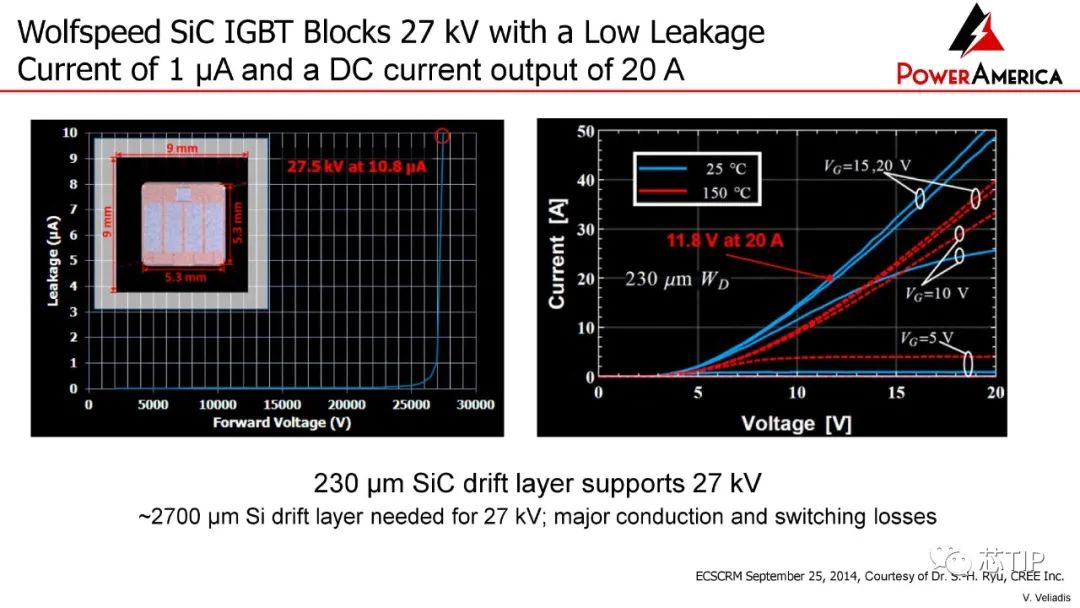

# Wolfspeed SiC IGBT 27 kV,具有 1 μA 的低漏電流和 20 A 的直流電流輸出

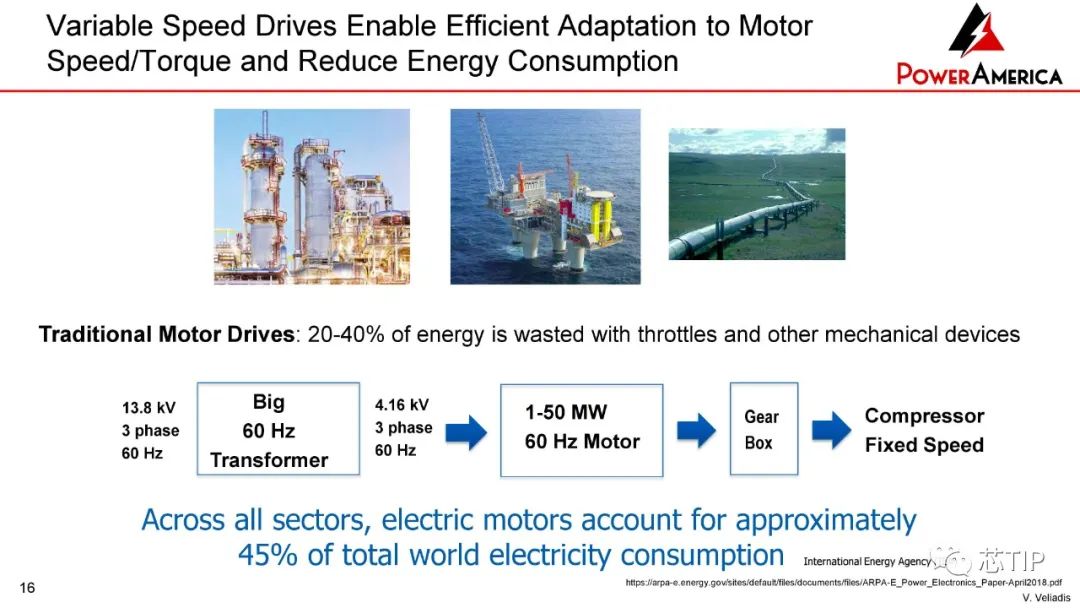

# 變速驅動器可有效適應電機速度/扭矩并降低能耗

(傳統電機驅動:20-40% 的能量被節流閥和其他機械裝置浪費)

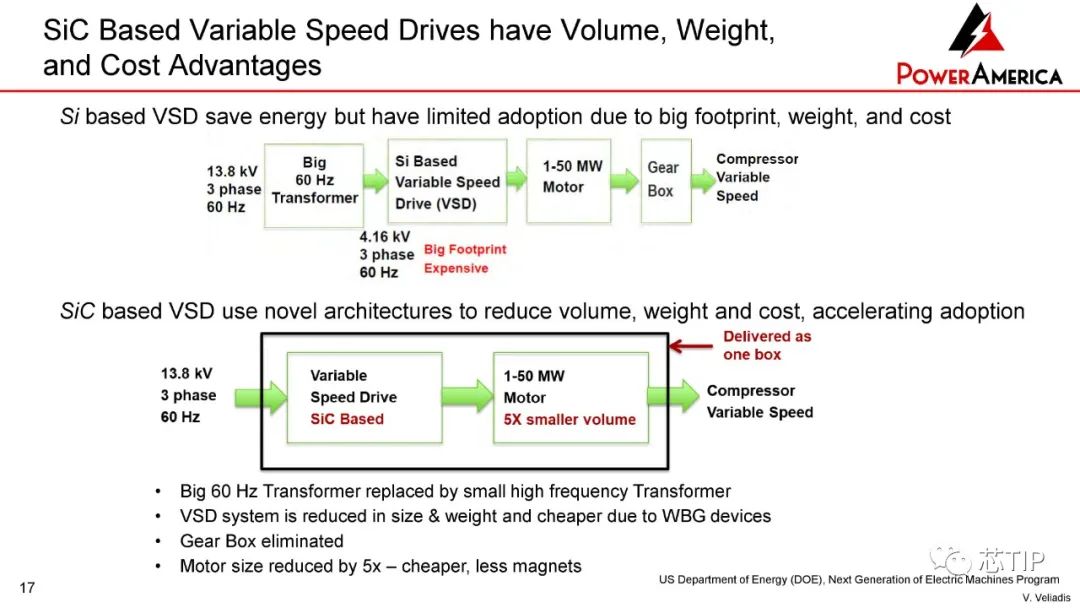

# 基于 SiC 的變速驅動器具有體積、重量和成本優勢

基于Si的VSD可節省能源,但由于占用空間大、重量大和成本高,采用率有限

基于 SiC的VSD使用新穎的架構來減少體積、重量和成本,采用率提升

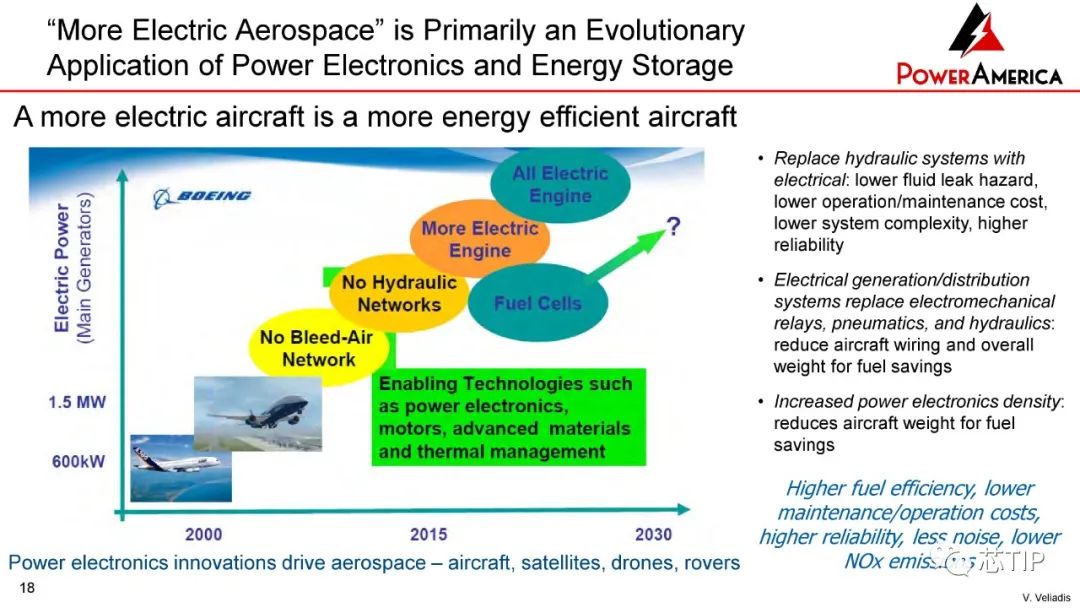

# 電力電子創新推動航空航天——飛機、衛星、無人機等

更高的燃油效率、更低的維護/運營成本、更高的可靠性、更低的噪音、更低的氮氧化物排放

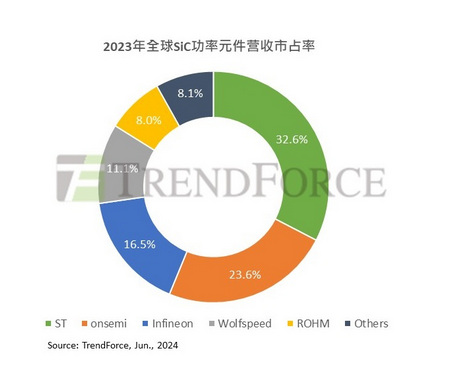

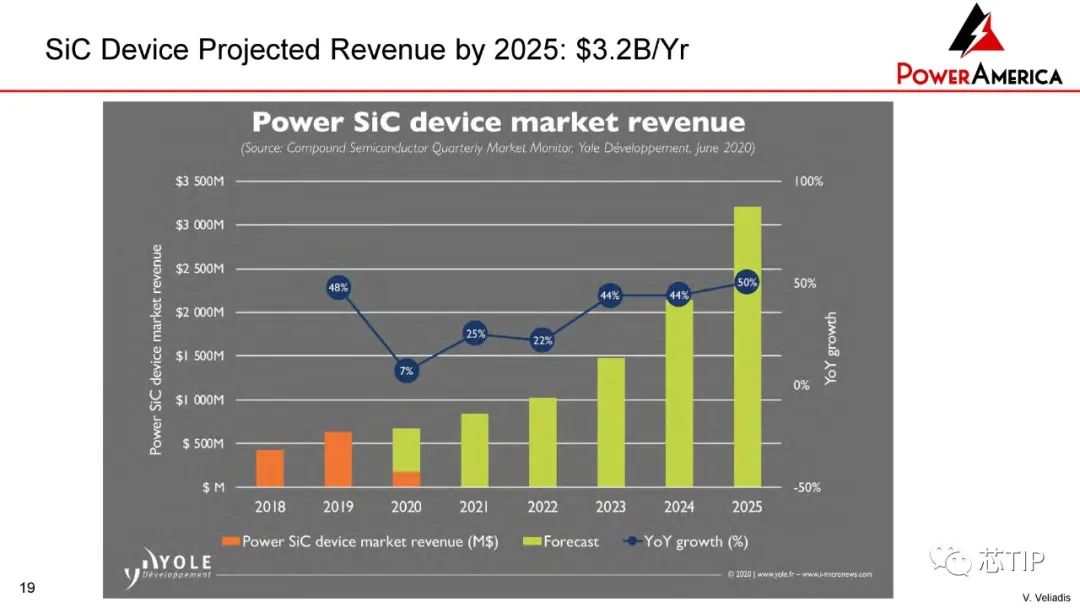

# 到 2025 年 SiC 器件預計收入:$3.2B/Yr

# SiC襯底的生長比Si更復雜

(與傳統硅功率器件制作工藝不同的是,碳化硅功率器件不能直接制作在碳化硅單晶材料上,必須在導通型單晶襯底上額外生長高質量的外延材料,并在外延層上制造各類器件)

# 碳化硅外延技術成熟度相對較高

# SiC 晶圓占 SiC 器件成本的 50-70%

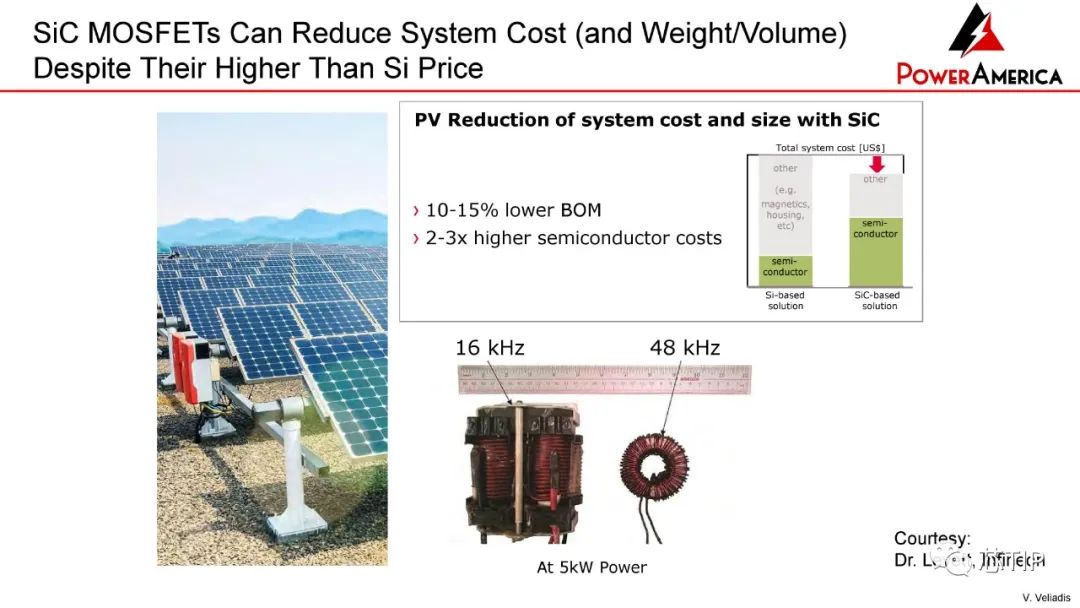

# SiC MOSFET 可以降低系統成本(和重量/體積),盡管它們的價格高于 Si

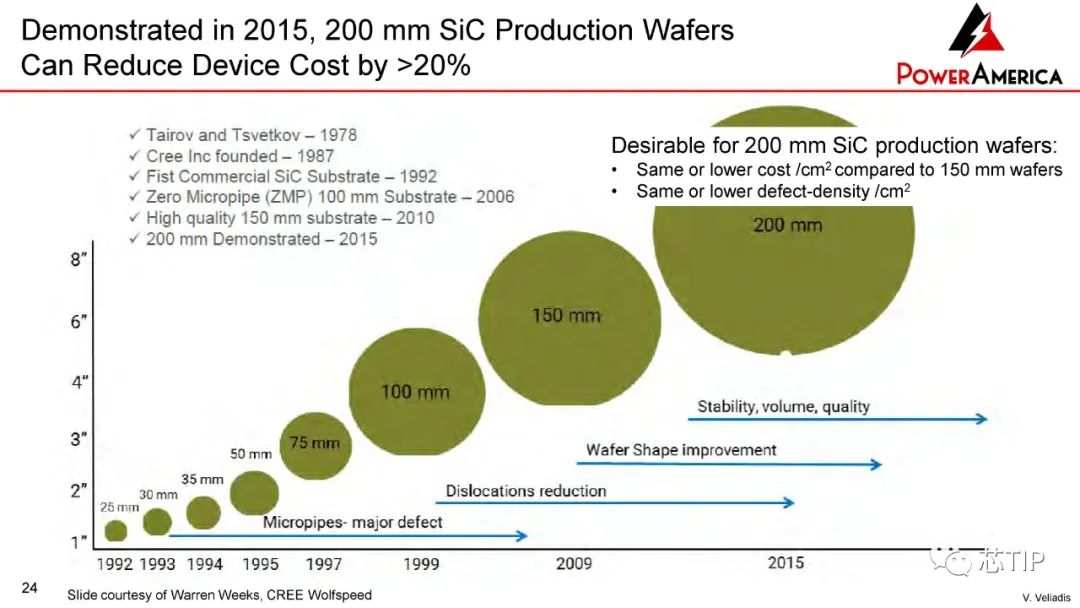

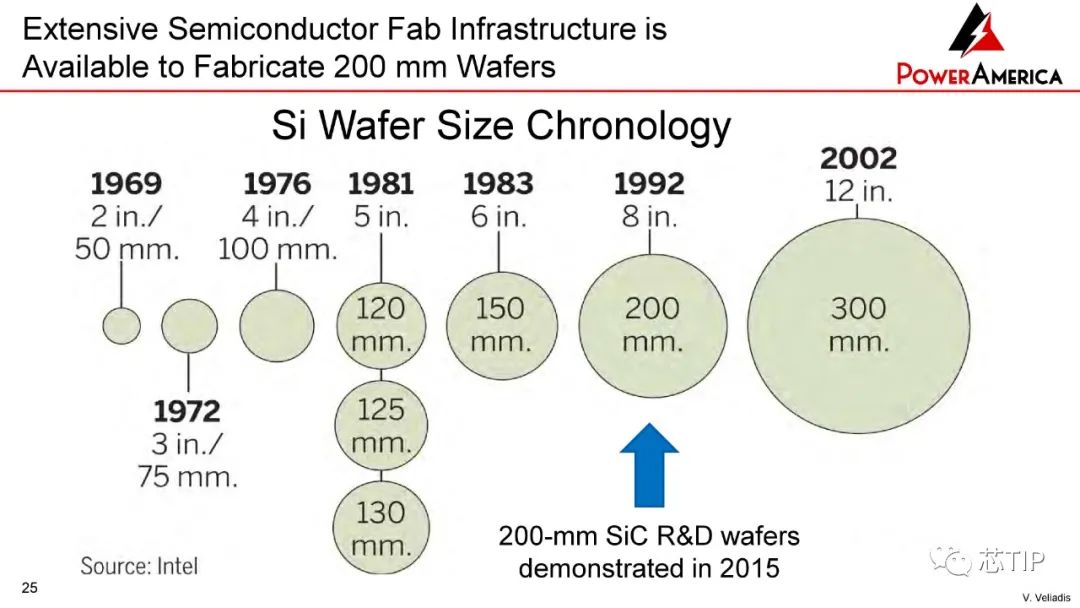

# 200 mm SiC 生產晶圓可將器件成本降低 >20%

# 大量半導體工廠可用于制造200mm晶圓

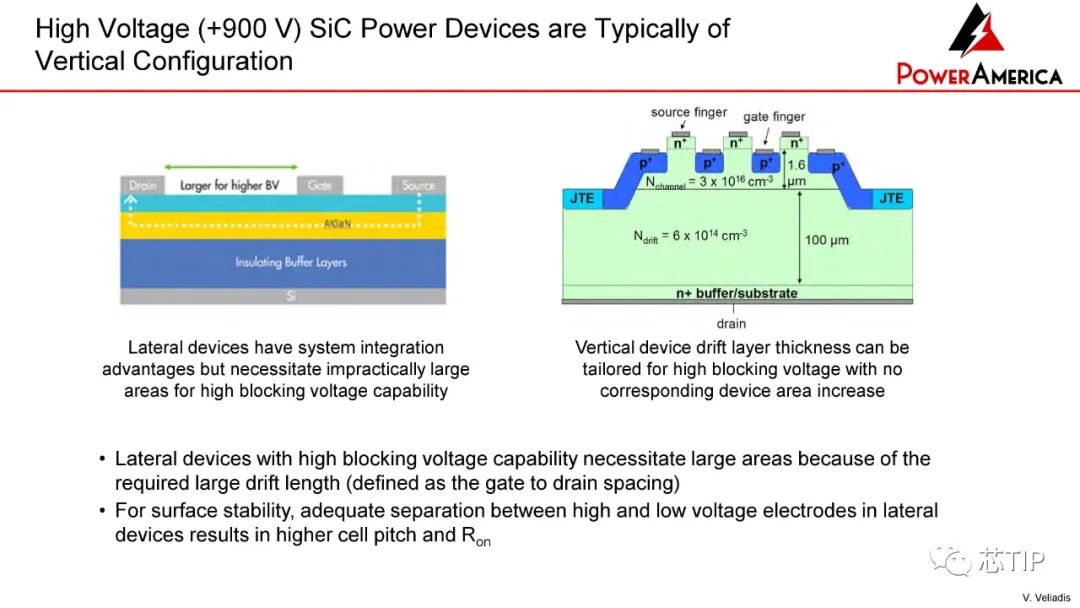

# 高壓 (+900 V) SiC 功率器件通常采用縱向配置

橫向器件具有系統集成優勢,但需要大面積以實現高阻斷電壓能力;

縱向器件漂移層厚度可以針對高阻斷電壓進行定制,而不會增加相應的器件面積;

由于需要較大的漂移長度(定義為柵極到漏極的間距),具有高阻斷電壓能力的橫向器件需要大面積;

對于表面穩定性,橫向器件中高壓和低壓電極之間的充分分離會導致更高的單元間距和導通電阻Ron。

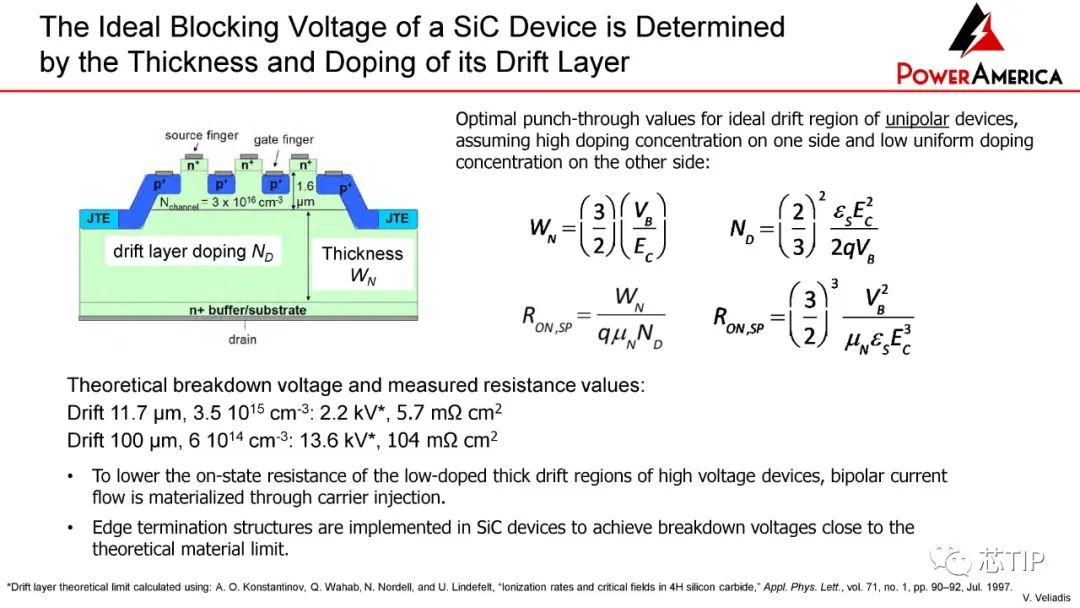

# SiC 器件的理想阻斷電壓由其漂移層的厚度和摻雜決定

為了降低高壓器件的低摻雜厚漂移區的導通電阻,雙極電流通過載流子注入實現;

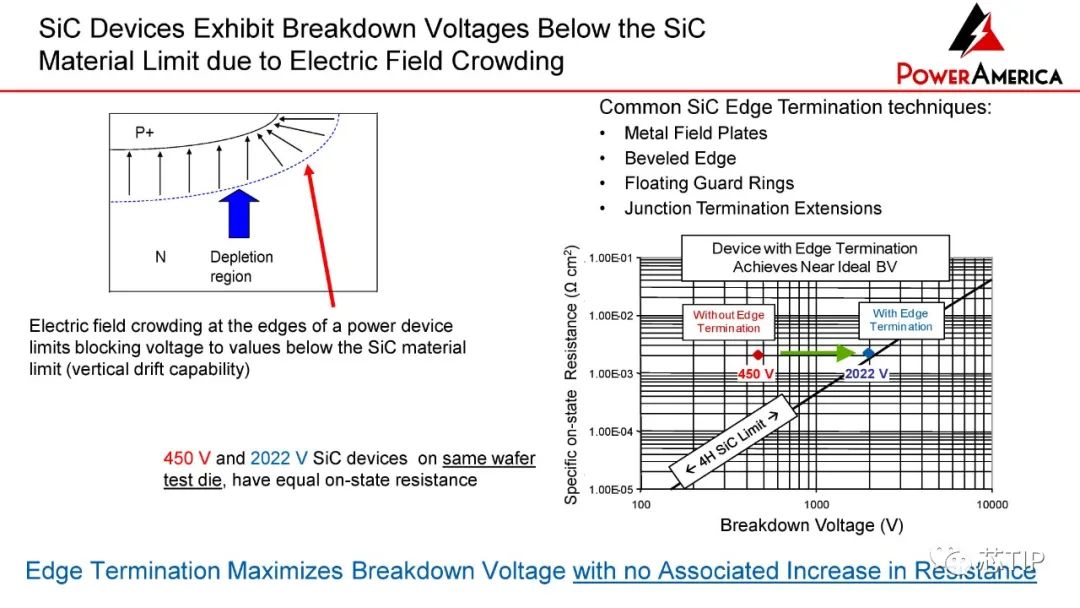

在SiC器件中實施邊緣終止結構,以實現接近理論材料極限的擊穿電壓。

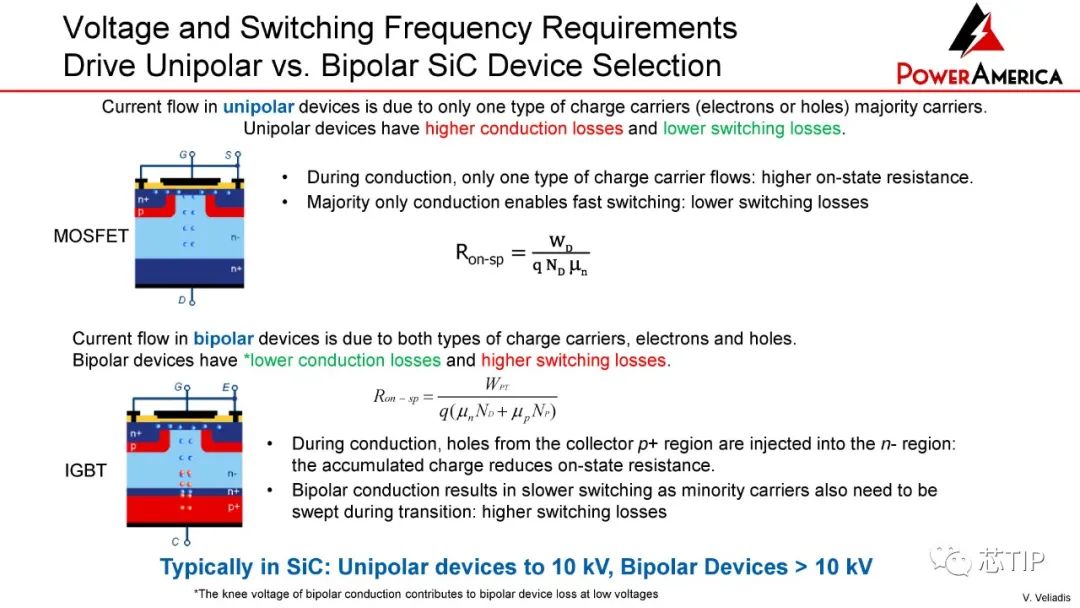

# 電壓和開關頻率需求推動單極與雙極 SiC 器件的選擇

單極器件中的電流僅歸因于一種類型的電荷載流子(電子或空穴)多數載流子

單極器件具有較高的傳導損耗和較低的開關損耗

在傳導過程中,只有一種類型的電荷載流子流動:更高的導通電阻

僅多數導通可實現快速開關:降低開關損耗

雙極器件中的電流是由兩種類型的電荷載流子、電子和空穴引起的

雙極器件具有更低的傳導損耗和更高的開關損耗

在導通過程中,來自集電極 p+ 區的空穴被注入到 n- 區:累積的電荷降低了導通電阻

雙極導通導致開關速度變慢,因為少數載流子在轉換期間也需要被掃描:更高的開關損耗

通常在 SiC 中:單極器件至 10 kV,雙極器件 > 10 kV

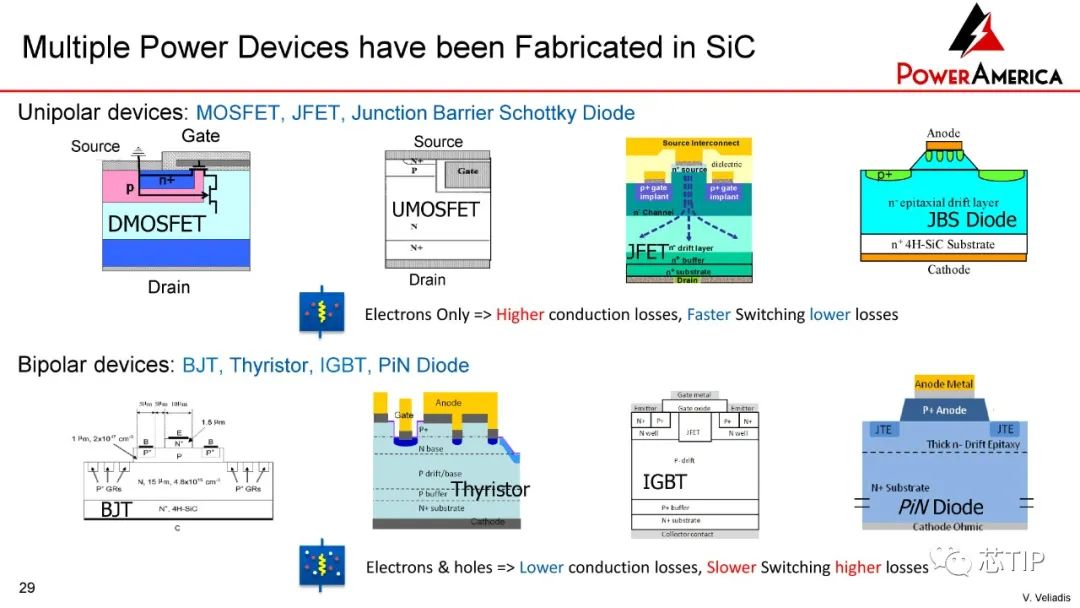

# SiC已經應用在多種器件中

單極器件:MOSFET、JFET、結勢壘肖特基二極管

雙極器件:BJT、晶閘管、IGBT、PiN 二極管

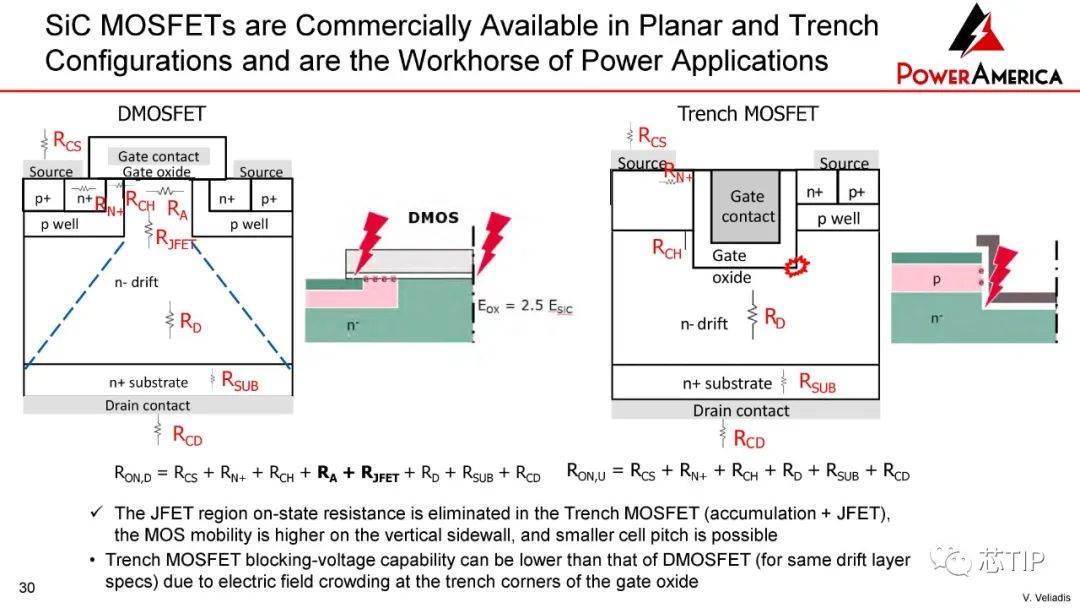

# SiC-MOSFET有平面型與溝槽型,是電力電子應用的主力軍

由于柵極氧化物的溝槽角處的電場擁擠,溝槽型MOSFET 的阻斷電壓能力可能低于 DMOSFET

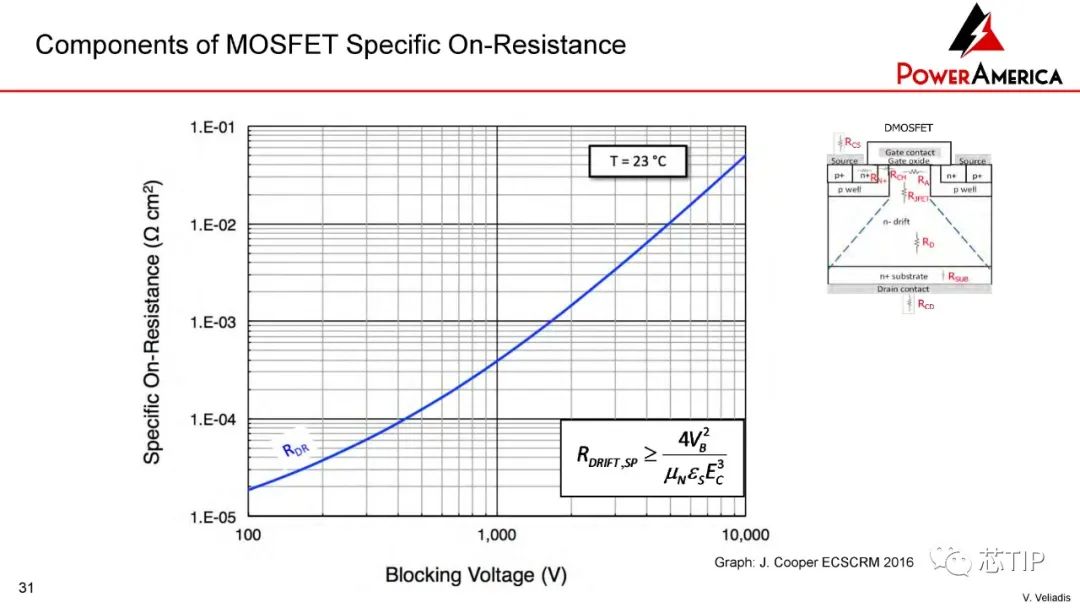

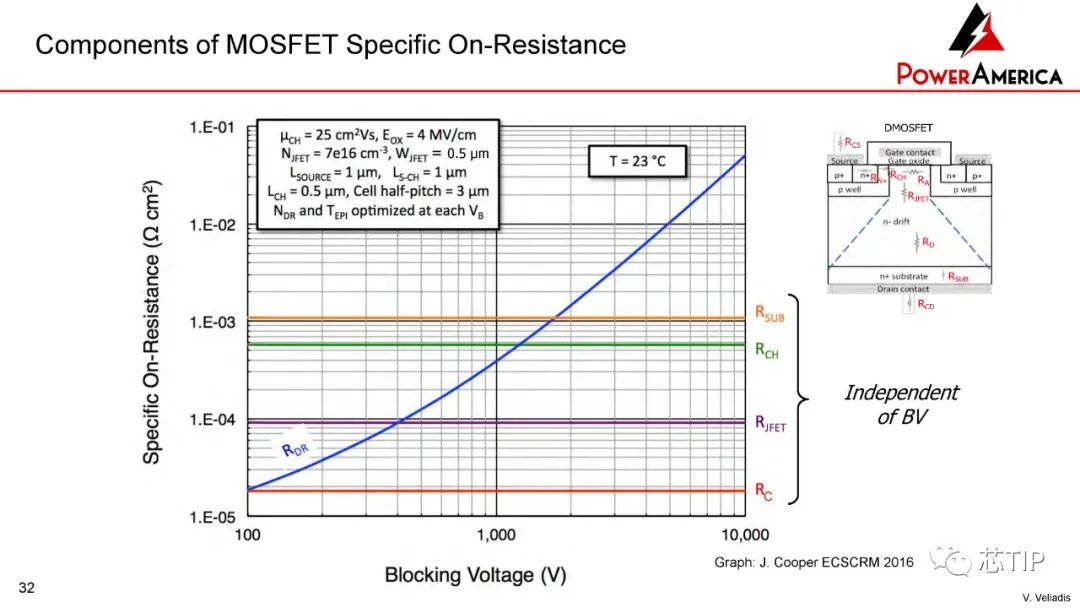

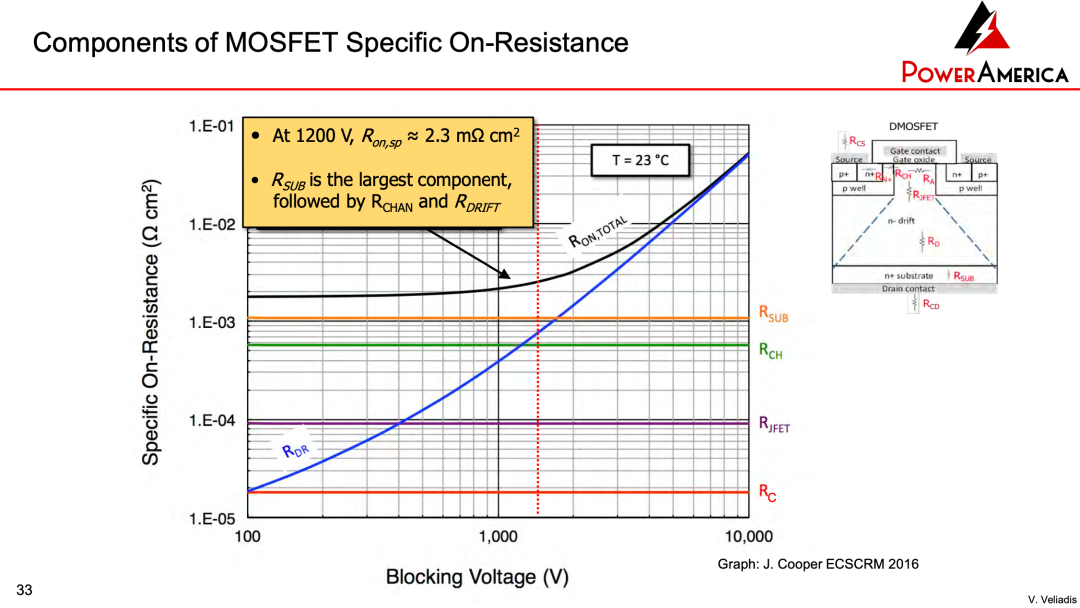

# MOSFET 特定導通電阻的組成部分

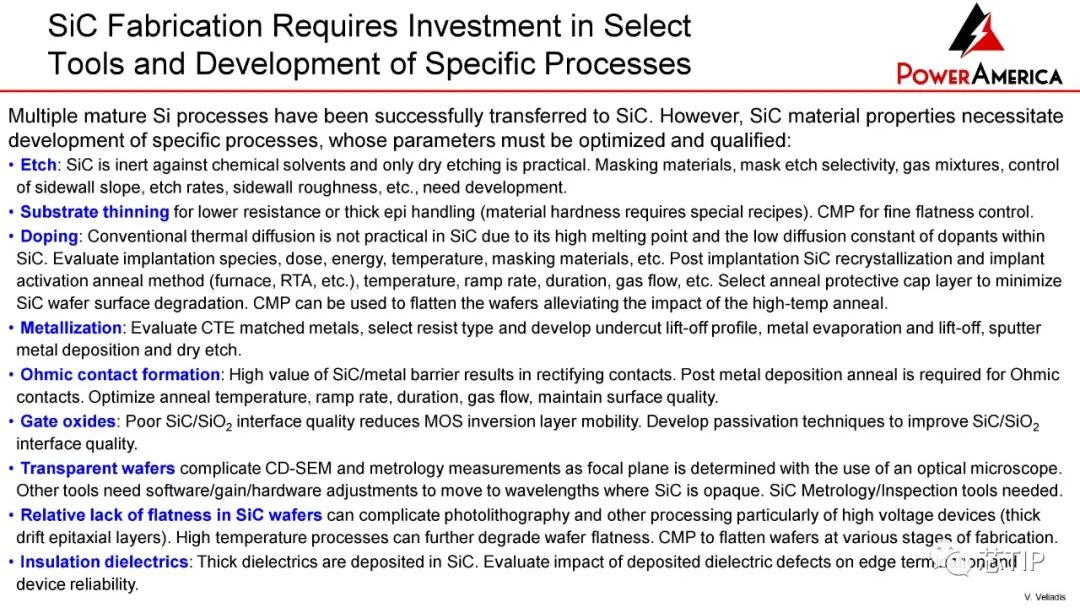

# SiC制造需要特定的設備和開發特定的工藝

多個成熟的 Si 工藝已成功轉移到 SiC。然而,碳化硅材料特性需要開發特定的工藝,其參數必須優化和合格:

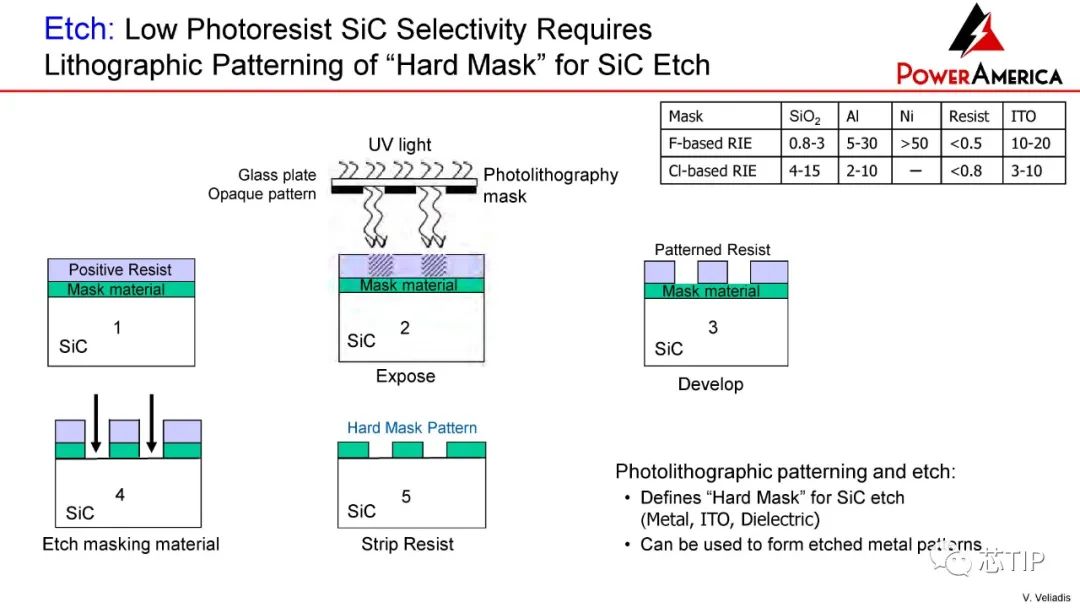

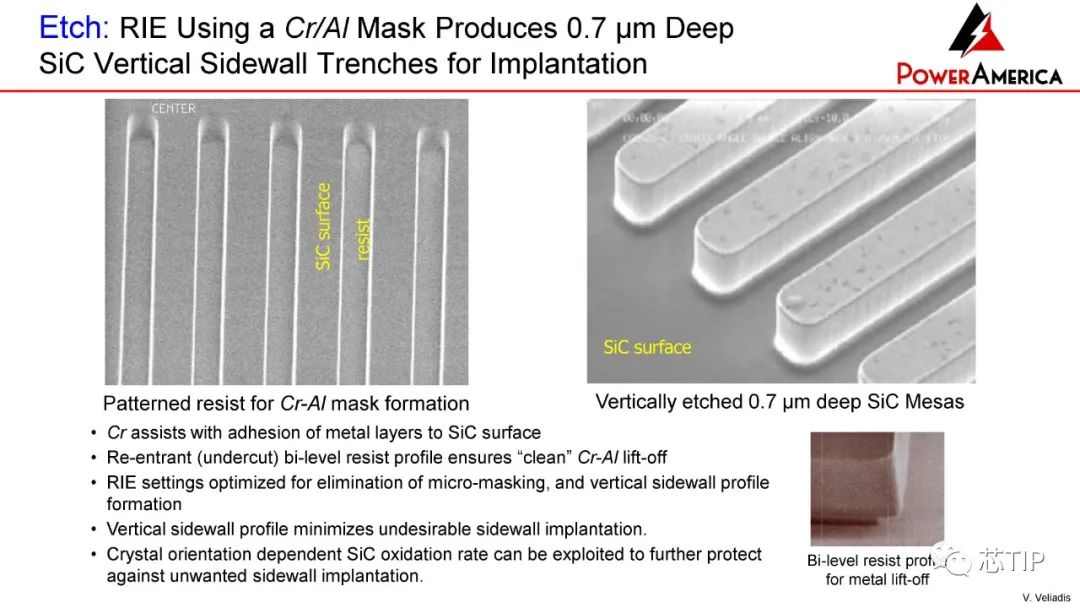

蝕刻:碳化硅對化學溶劑是惰性的,只有干蝕刻是可行的。掩膜材料、掩膜蝕刻選擇性、氣體混合物、側壁斜率的控制、蝕刻速率、側壁粗糙度等都需要開發。

用于降低電阻或厚外延處理的基板減薄(材料硬度需要特殊配方)。用于精細平面度控制的 CMP。

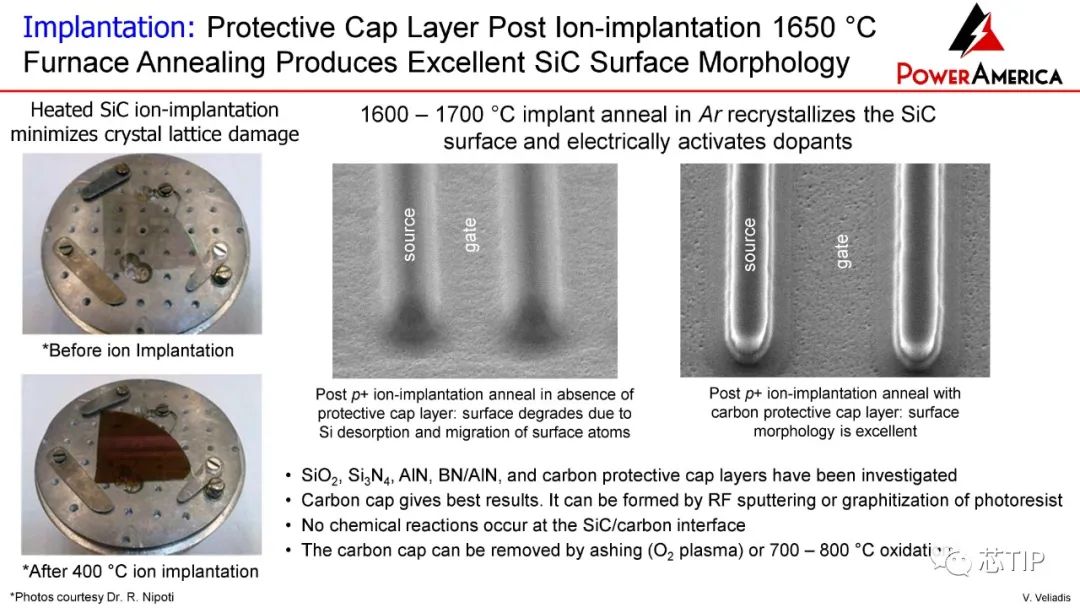

摻雜:傳統的熱擴散在 SiC 中不實用,因為它具有高熔點和 SiC 內摻雜劑的低擴散常數。評估注入種類、劑量、能量、溫度、掩膜材料等。注入后 SiC 再結晶和注入激活退火方法(熔爐、RTA 等)、溫度、升溫速率、持續時間、氣體流量等。選擇退火保護層以最大限度地減少 SiC 晶片表面退化。CMP 可用于使晶圓變平以減輕高溫退火的影響。

金屬化:評估 CTE 匹配的金屬,選擇抗蝕劑類型、金屬蒸發和剝離、濺射金屬沉積和干法蝕刻。

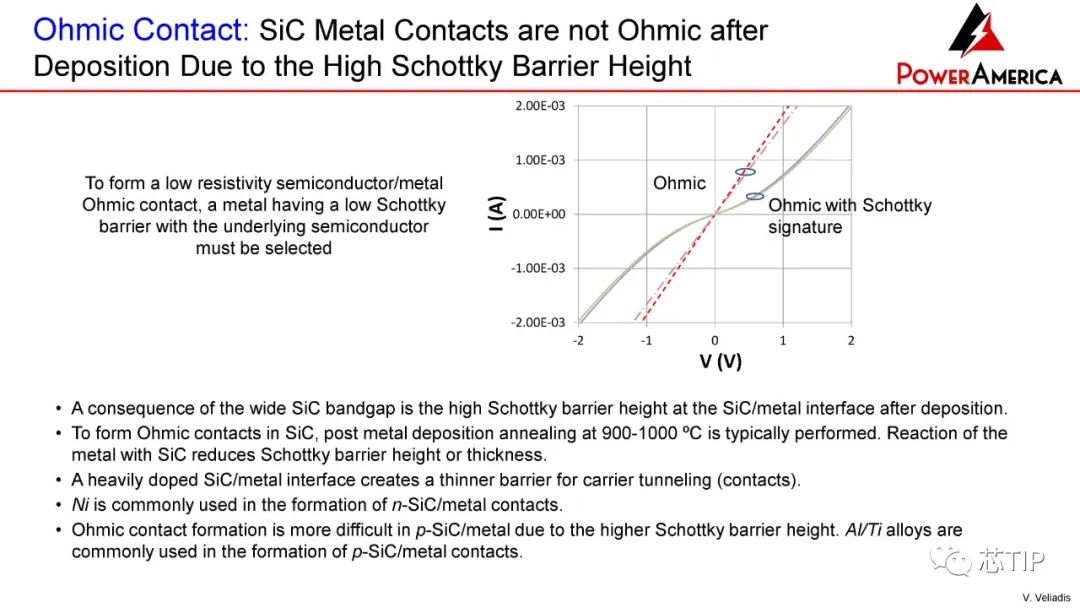

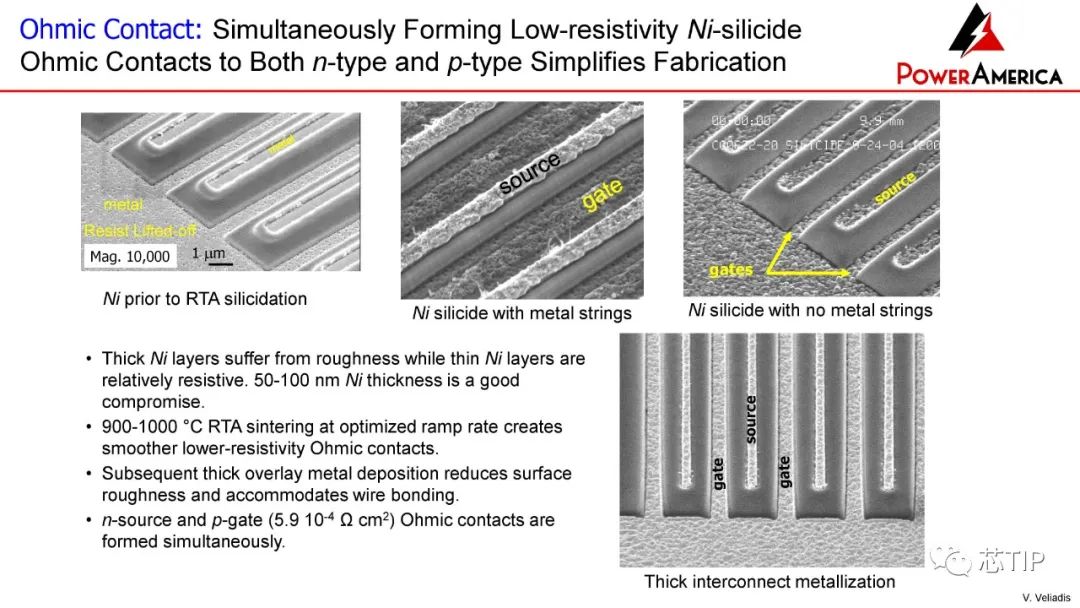

歐姆接觸形成:SiC/金屬阻擋層的高值導致整流接觸。歐姆接觸需要后金屬沉積退火。優化退火溫度、升溫速率、持續時間、氣體流量,保持表面質量。

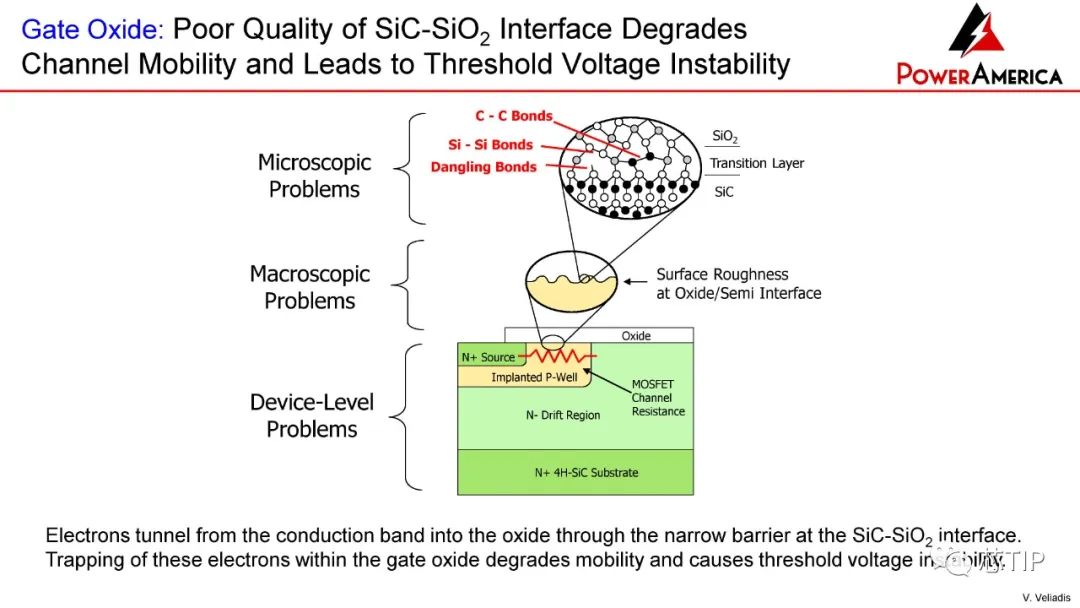

柵極氧化物:不良的 SiC/SiO2 界面質量會降低 MOS 反型層遷移率。開發鈍化技術以提高 SiC/SiO2 界面質量。

透明的晶圓使CD-SEM和計量測量變得復雜,因為焦平面是用光學顯微鏡來確定的。其他工具需要軟件/增益/硬件調整,以適應 SiC 不透明的波長。需要 SiC 計量/檢測工具。

SiC晶圓相對缺乏平整度會使光刻和其他加工變得復雜,特別是高壓設備(厚漂移外延層)。高溫工藝會進一步降低晶圓的平整度。CMP可以在制造的各個階段使晶圓平整。

絕緣電介質:厚電介質沉積在 SiC 中。評估沉積的介電缺陷對邊緣端接和器件可靠性的影響。

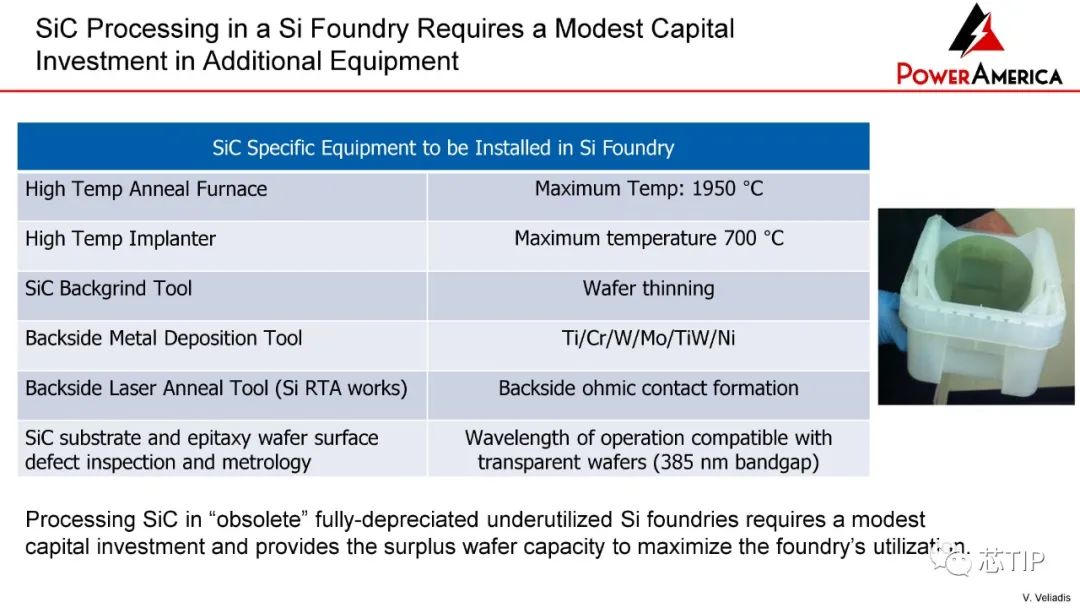

# SiC 加工需要對附加設備進行適度的成本投資

(在完全折舊未充分利用的硅晶圓代工廠中加工 SiC 需要適度的成本投資,并提供剩余的晶圓產能以最大限度地提高代工廠的利用率。)

# 蝕刻:反應性離子蝕刻(RIE)通常用于在 SiC 中形成臺面結構和溝槽

# 蝕刻:低光刻膠 SiC 選擇性需要光刻圖案化“硬掩模”用于 SiC 蝕刻

# 蝕刻:使用 Cr/Al 掩模的 RIE 產生 0.7 μm 深的 SiC 垂直側壁溝槽用于植入

# 歐姆接觸:由于高肖特基勢壘高度,SiC 金屬接觸在沉積后不是歐姆接觸

# 歐姆接觸:同時形成 n 型和 p 型的低電阻率硅化鎳歐姆接觸簡化了制造

# 注入:離子注入是實用的SiC選擇性摻雜技術,然后在~1600℃的爐中退火

# 注入:離子注入后的保護帽層 1650 °C 爐退火產生出色的 SiC 表面形貌

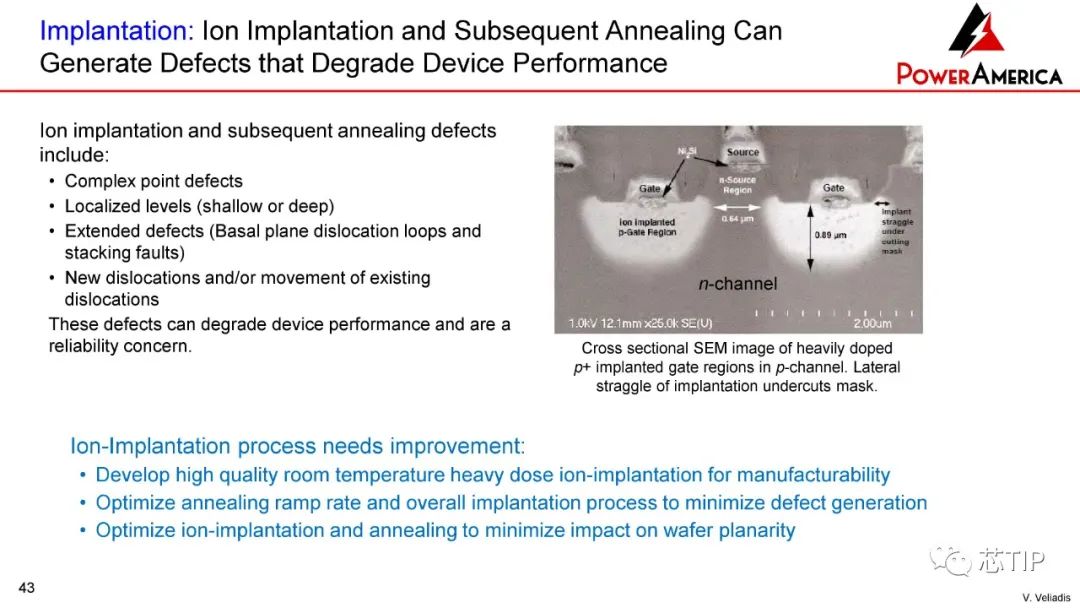

# 注入:離子注入和隨后的退火會產生降低設備性能的缺陷

離子注入工藝需要改進:

? 開發可制造的高質量室溫大劑量離子注入

? 優化退火升溫速率和整體注入工藝,以最大限度地減少缺陷的產生

? 優化離子注入和退火,以盡量減少對晶圓平面度的影響

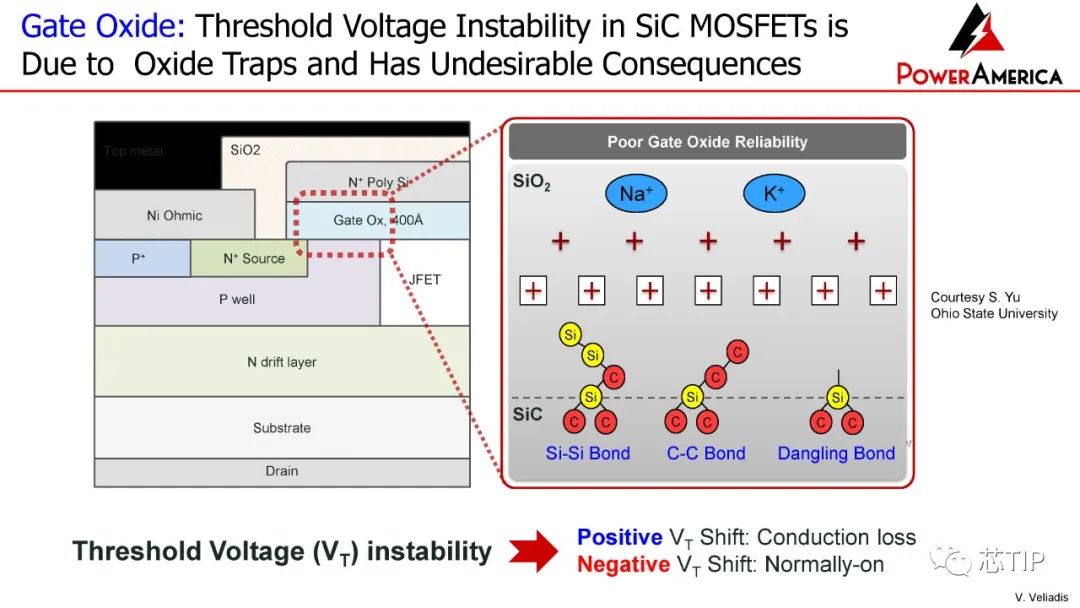

# 柵極氧化物:SiC-SiO2 界面質量差會降低溝道遷移率并導致閾值電壓不穩定

電子通過 SiC-SiO2 界面處的窄勢壘從導帶隧穿到氧化物中,將這些電子俘獲在柵極氧化物中會降低遷移率并導致閾值電壓不穩定。

# 柵極氧化物:SiC MOSFET 中的閾值電壓不穩定性是由氧化物陷阱引起的,并具有不良后果

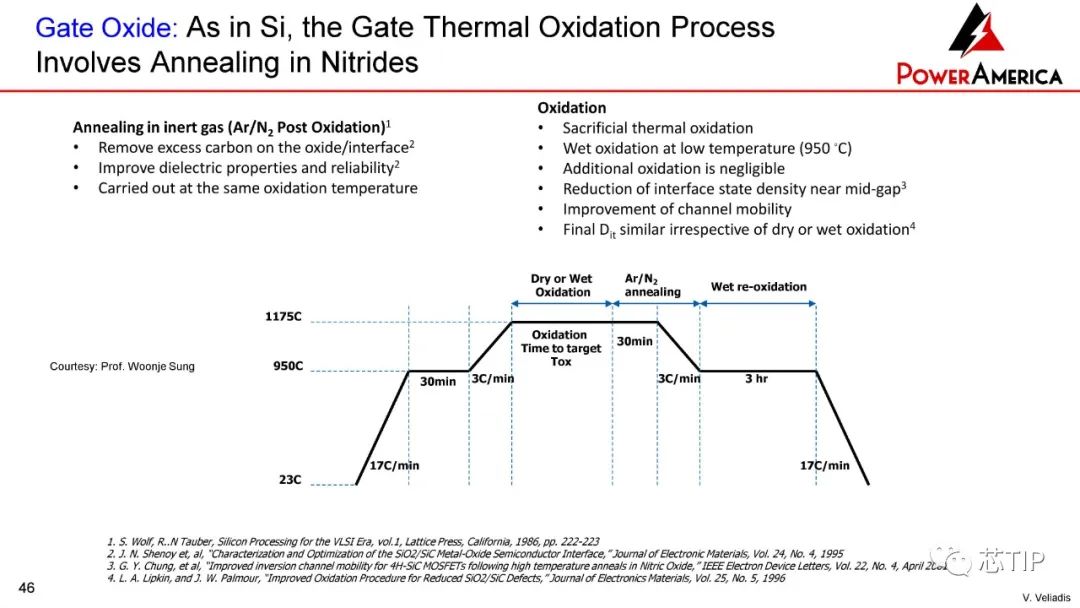

# 柵極氧化物:與 Si 一樣,柵極熱氧化過程涉及氮化物的退火

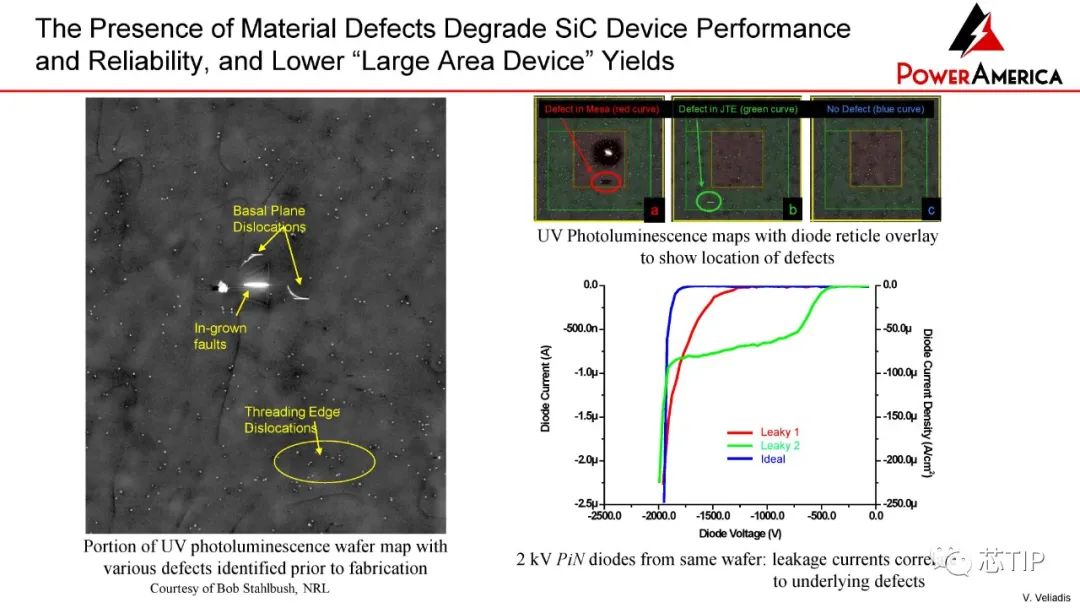

# 材料缺陷的存在會降低 SiC 器件的性能和可靠性,并降低“大面積器件”的良率

# 由于電場擁擠,SiC 器件的擊穿電壓低于 SiC 材料極限

參考來源:

Dr. Victor Veliadis

Deputy Executive Director and CTO, PowerAmerica

Professor ECE North Carolina State University, Raleigh, NC USA

部分編譯:芯TIP@吳晰

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。