- 基于verilog的FPGA編程經驗總結-用了半個多月的ISE,幾乎全是自學起來的,碰到了很多很多讓人DT好久的小問題,百度也百不到,后來還是都解決了,為了盡量方便以后的剛學ISE的童鞋不再因為一些小問題而糾結,把這幾天的經驗總結了一下。好了,廢話不多說,上料!

- 關鍵字:

verilog FPGA

- verilog語言實現任意分頻-原文出自:分頻器是指使輸出信號頻率為輸入信號頻率整數分之一的電子電路。在許多電子設備中如電子鐘、頻率合成器等,需要各種不同頻率的信號協同工作,常用的方法是以穩定度高的晶體振蕩器為主振源,通過變換得到所需要的各種頻率成分,分頻器是一種主要變換手段。

- 關鍵字:

verilog 分頻器 電子電路

- 深入分析verilog阻塞和非阻塞賦值-學verilog 一個月了,在開發板上面寫了很多代碼,但是始終對一些問題理解的不夠透徹,這里我們來寫幾個例子仿真出阻塞和非阻塞的區別

- 關鍵字:

verilog 阻塞 非阻塞

- Verilog HDL簡明教程(2)-模塊是Verilog 的基本描述單位,用于描述某個設計的功能或結構及其與其他模塊通信的外部端口。

- 關鍵字:

Verilog HDL

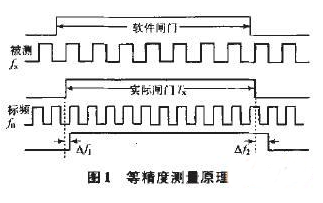

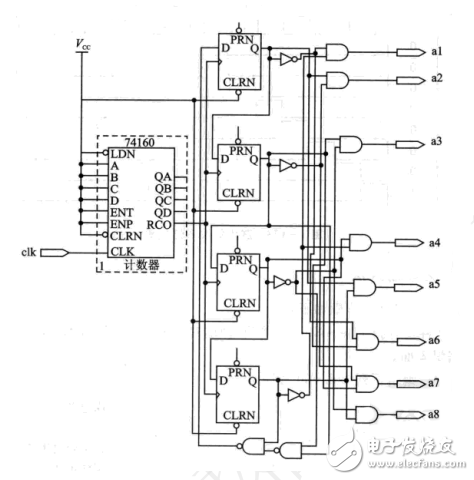

- 引言 傳統測量頻率的方法主要有直接測量法、分頻測量法、測周法等,這些方法往往只適用于測量一段頻率,當被測信號的頻率發生變化時,測量的精度就會下降。本文提出一種基于等精度原理的測量頻率的方法,在整個頻率測量過程中都能達到相同的測量精度,而與被測信號的頻率變化無關。本文利用FPGA(現場可編程門陣列)的高速數據處理能力,實現對被測信號的測量計數;利用單片機的運算和控制能力,實現對頻率、周期、脈沖寬度的計算及顯示。 等精度測量原理等精度測量的一個最大特點是測量的實際門控時間不是一個固定值,而

- 關鍵字:

Verilog FPGA

- 1 功能概述 流水廣告燈主要應用于LED燈光控制。通過程序控制LED的亮和滅, 多個LED燈組成一個陣列,依次逐個點亮的時候像流水一樣,所以叫流水燈。由于其形成美觀大方的視覺效果,因此廣泛應用于店鋪招牌、廣告、大型建筑夜間裝飾、景觀裝飾等。 在FPGA電路設計中,盡管流水燈的設計屬于比較簡單的入門級應用,但是其運用到的方法,是FPGA設計中最核心和最常用部分之一,是FPGA設計必須牢固掌握的基礎知識。從這一步開始,形成良好的設計習慣,寫出整潔簡潔的代碼,對于FPGA設計師來說至

- 關鍵字:

Verilog FPGA

- Verilog HDL 不僅提供描述設計的能力,而且提供對激勵、控制、存儲響應和設計驗證的建模能力。激勵和控制可用初始化語句產生。驗證運行過程中的響應可以作為 “ 變化時保存 ” 或作為選通的數據存儲。最后,設計驗證可以通過在初始化語句中寫入相應的語句自動與期望的響應值比較完成。

- 關鍵字:

Verilog HDL 設計模擬

- 以前的數字邏輯電路及系統的規模的比較小而且簡單,用電路原理圖輸入法基本足夠了。但是一般工程師需要手工布線,需要熟悉器件的內部結構和外部引線特點,才能達到設計要求,這個工作量和設計周期都不是我們能想象的。現在設計要求的時間和周期都很短,用原理圖這個方法顯然就不符合實際了。

- 關鍵字:

Verilog HDL 虛擬接口聯盟

- 線網類型。 net type 表示 Verilog 結構化元件間的物理連線。它的值由驅動元件的值決定,例如連續賦值或門的輸出。如果沒有驅動元件連接到線網,線網的缺省值為 z 。

- 關鍵字:

Verilog 數據類型

- Verilog HDL 中的標識符 (identifier) 可以是任意一組字母、數字、 $ 符號和 _( 下劃線 ) 符號的組合,但標識符的第一個字符必須是字母或者下劃線。另外,標識符是區分大小寫的。

- 關鍵字:

Verilog 語言要素 VHDL

- HDL 語言在國外有上百種。高等學校、科研單位、 EDA 公司都有自己的 HDL 語言。現選擇較有影響的作簡要介紹。

- 關鍵字:

HDL VHDL 種類

- 這兩種語言都是用于數字電子系統設計的硬件描述語言,而且都已經是 IEEE 的標準。 VHDL 1987 年成為標準,而 Verilog 是 1995 年才成為標準的。這個是因為 VHDL 是美國軍方組織開發的,而 Verilog 是一個公司的私有財產轉化而來的。為什么 Verilog 能成為 IEEE 標準呢?它一定有其優越性才行,所以說 Verilog 有更強的生命力。

- 關鍵字:

Verilog VHDL HDL

- FPGA(Field Pmgrammable Gate Array)現場可編程門陣列在數字電路的設計中已經被廣泛使用。這種設計方式可以將以前需要多塊集成芯片的電路設計到一塊大模塊可編程邏輯器件中,大大減少了電路板的尺寸,增強了系統的可靠性和設計的靈活性。本文詳細介紹了已在實際項目中應用的基于FPGA的串口通訊設計。本設計分為硬件電路設計和軟件設計兩部分,最后用仿真驗證了程序設計的正確性。

- 關鍵字:

Verilog 串口通訊 FPGA

- 本文設計的系統采用PLX公司生產的CPCI協議轉換芯片PCI9054,通過Verilog HDL語言在FPGA中產生相應的控制信號,完成對數據的快速讀寫,從而實現了與CPCI總線的高速數據通信。

- 關鍵字:

CPCI協議轉換 Verilog FPGA

- 1 引言近年來,由于微電子學和計算機技術的迅速發展,給EDA技術行業帶來了巨大的變化。 HDL(hardware description language)硬件描述語言是一種描述電路行為的

- 關鍵字:

Verilog CPLD FPGA HDL 漢明碼

verilog hdl介紹

Verilog HDL是一種硬件描述語言(HDL:Hardware Discription Language),是一種以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。

Verilog HDL和VHDL是目前世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。前者由Gateway Design Aut [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473