- 實現世界上最先進的定制邏輯器件引言

Altera于2008年第二季度推出Stratix® IV和HardCopy® IV器件系列標志著世界上首款40-nm FPGA和業界唯一

40-nm ASIC 無風險移植途徑的誕生。Altera 通過三年周密的規劃和

- 關鍵字:

40 nm 工藝 定制

- SMT小型電子產品的安裝是高等職業學校應用電子技術專業中《電子產品工藝實訓》課程的一個重要項目。結合《電子產品工藝》這門課程的特點,我們在電子實訓環節采用了項目教學模式,即師生雙方共同在實訓室參與項目教學

- 關鍵字:

環節 應用 工藝 電子 教學 項目

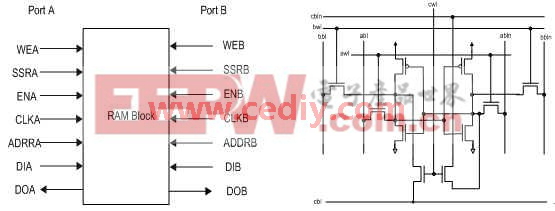

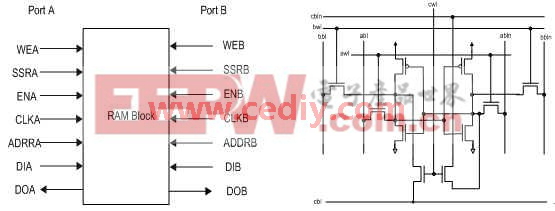

- 基于0.13微米CMOS工藝下平臺式FPGA中可重構RAM模塊的一種設計方法,1. 引言

對于需要大的片上存儲器的各種不同的應用,FPGA 需要提供可重構且可串聯的存儲器陣列。通過不同的配置選擇,嵌入式存儲器陣列可以被合并從而達到位寬或字深的擴展并且可以作為單端口,雙端口

- 關鍵字:

RAM 重構 模塊 設計 方法 FPGA 平臺 0.13 微米 CMOS 工藝

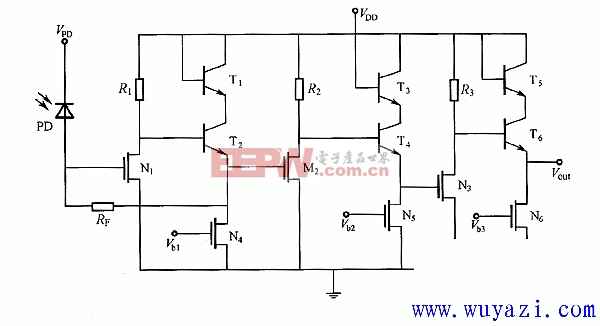

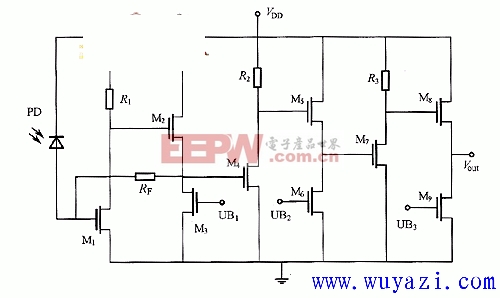

- 0 引言

運算放大器是數據采樣電路中的關鍵部分,如流水線模數轉換器等。在此類設計中,速度和精度是兩個重要因素,而這兩方面的因素都是由運放的各種性能來決定的。

本文設計的帶共模反饋的兩級高增益運

- 關鍵字:

CMOS 工藝 放大器 全差分

- 針對DC-DC電源管理系統中所必須的欠壓鎖存(UVLO)功能,提出一種改進的欠壓鎖存電路。所設計的電路在不使用額外的帶隙基準電壓源作為比較基準的情況下,實現了閾值點電位、比較器的滯回區間等參量的穩定。整個電路采用CSMC0.5 μm BCD工藝設計,使用HSpice軟件仿真,結果表明所設計的UVLO電路具有結構簡單、反應靈敏、溫度漂移小、功耗低等特點。

- 關鍵字:

電路設計 工藝 BCD 基于

- 半導體設備和材料企業的技術提升及創新要從研究材料入手,從源頭上達到國際先進水平。在工業制備方面要加強新型工藝的開發和應用。我國半導體設備性能、控制已達到國際高端水平,但穩定性還待提升。另外,需要做高端設備工藝方面的提升和研究。

蘭州瑞德自主開發的產品涉及多行業、多領域,在國際金融危機期間,遇到的問題主要在工藝應用和需求行業比例發生變化方面,公司根據各行業特點,公司采取新品上市、設備改制、設備派生等手段,使研、切、拋電子專用設備進入各行業的速度加快了,尤其是視窗、光學等行業。半導體行業仍主打高端設

- 關鍵字:

半導體設備 工藝

- 近年來,軟件無線電(Software Radio)的技術受到廣泛的關注。理想的軟件無線電臺要求對天線接收的模擬信號經過放大后直接采樣,但是由于通常射頻頻率(GHz頻段)過高,技術上所限難以實現,而多采用中頻采樣的方法。而對

- 關鍵字:

Telescopic 0.13 CMOS 工藝

- 基于美國聯邦通訊委員會(FCC)的E911定向和定位業務(LBS),期望緊跟這一標準的全球定位系統(GPS)接收機隨時準備在無線通信中扮演一個至關重要的角色。成功的E911/LBS產品與業務將會需要具有以下特征的解決方案:能在移

- 關鍵字:

SiGe GPS 工藝 接收機

- 從現有市場行情來看,國內多晶硅價格下跌的趨勢將難以改變。國內可將生產成本壓低到50美元/公斤以下的多晶硅企業,幾乎是鳳毛麟角。

森松集團(中國)(下稱“森松”)董事總經理薛絳穎接受記者專訪時表示,目前中國的多晶硅設備制造已較為成熟。而國內多晶硅生產商的管理、技術及工藝都有待提高,這樣才能有效控制成本。

裝備技術尤為關鍵。以森松集團為例,作為國內最大的多晶硅工藝成套設備供應商,約有80%的國內多晶硅廠,都使用其成套設備如還原爐以及相關技術。

該公司生產的還原爐要

- 關鍵字:

工藝 多晶硅

- 新華網北京3月27日電記者 27日從科技部獲悉,我國“極大規模集成電路制造裝備及成套工藝”重大專項進入全面實施階段?

據介紹,“極大規模集成電路制造裝備及成套工藝”重大專項旨在開發集成電路關鍵制造裝備,掌握具有自主知識產權的成套先進工藝及相關新材料技術,打破我國高端集成電路制造裝備與工藝完全依賴進口的狀況,帶動相關產業的技術提升和結構調整?

重大專項是實現我國中長期科技發展規劃的一項重要內容,黨中央?國務院高度重視重大專項的實施工作,多次召開

- 關鍵字:

集成電路 工藝

- 應答器設計的成本依賴于幾個因素,而不僅僅是硅的成本。事實上,芯片制造工藝的成本(就其復雜性和成熟程度...

- 關鍵字:

功耗 低功耗 驅動 工藝 溫度 電壓

- 壓控振蕩器(VCO)是射頻集成電路(RF-ICs)中的關鍵模塊之一。近年來隨著無線通信技術的快速發展,射頻收發機也有了新的發展趨勢,即單個收發機要實現寬頻率多標準的覆蓋,例如用于移動數字電視接收的調諧器一般要實現T-DMB、DMB-T等多個標準,并能覆蓋VHF、UHF和LBAND等多個頻段。本文所介紹的VCO設計采用如圖1(a)所示的交叉耦合電感電容結構,相對于其他結構的VCO來說該結構更加易于片上集成和實現低功耗設計,并且利用LC諧振回路的帶通濾波特性,能獲得更好的相位噪聲性能。

- 關鍵字:

寬帶 LC VCO 設計 相噪 工藝 0.18 RF CMOS 基于

- 本文基于Peregrine(派更)半導體公司的單片數字步進衰減器(DSA,Digital Step Attenuator)產品系列,闡述了DSA通用設計方法、RF CMOS工藝以及這些器件的性能。

- 關鍵字:

CMOS 工藝 步進 數字

- IBM聯盟開發出可在32納米芯片中加速實現一種被稱為“high-k/metal gate(高電介質金屬柵極)”的突破性材料。這種新方法是基于被稱為“high-k gate-first(高電介質先加工柵極)”加工工藝的方法,為客戶轉向高電介質金屬柵極技術提供了一種更加簡單和更省時間的途徑,由此而能夠帶來的益處包括性能的提高和功耗的降低。通過使用高電介質金屬柵極,IBM與聯盟合作伙伴成功地開發出比上一代技術體積小50%的芯片,同時提高了眾多性能。使用這種新技術的

- 關鍵字:

制程 工藝

sf4x 工藝介紹

您好,目前還沒有人創建詞條sf4x 工藝!

歡迎您創建該詞條,闡述對sf4x 工藝的理解,并與今后在此搜索sf4x 工藝的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473